DISTRIBUTED BY:

.R. 186

MERIT ELECTRONICS, INC 2362 Oume Drive San Jose, GA 95131

108)434-08

# IC MEMORIES

All values shown in this catalogue are subject to change for product improvement.

The information, diagrams and all other data included herein are believed to be correct and reliable. However, no responsibility is assumed by Mitsubishi Electric Corporation for their use, nor for any infringements of patents or other rights belonging to third parties which may result from their use.

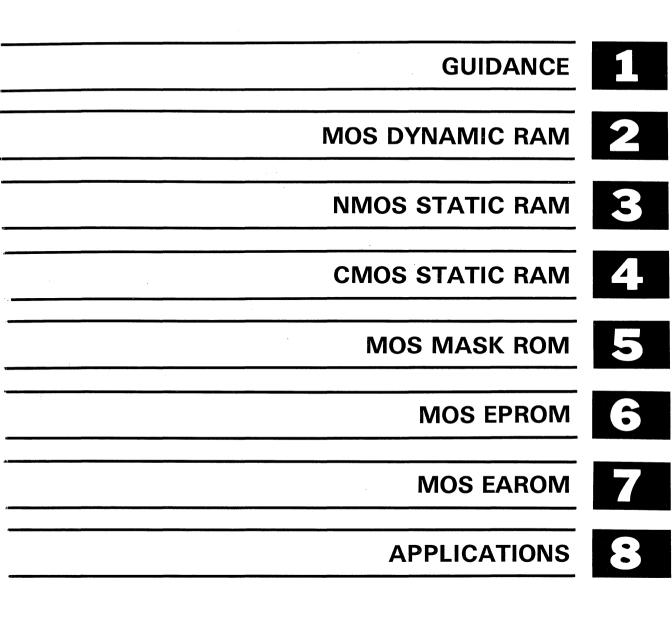

## 1

| GUIDANCE                                  | Page |

|-------------------------------------------|------|

| Guide to Selection of IC Memories         | 1—2  |

| Index by Function                         | 18   |

| Guide to Interchangeability               |      |

| Ordering Information                      | 1—18 |

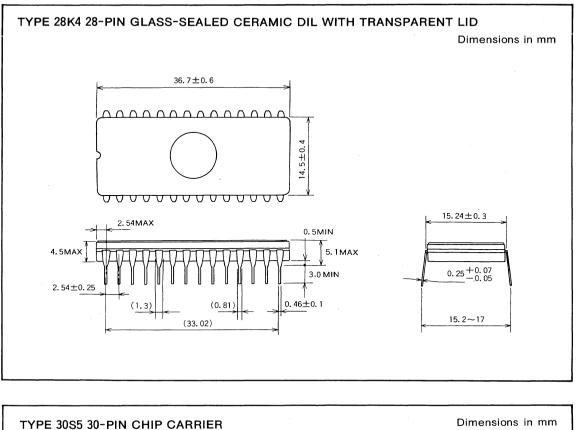

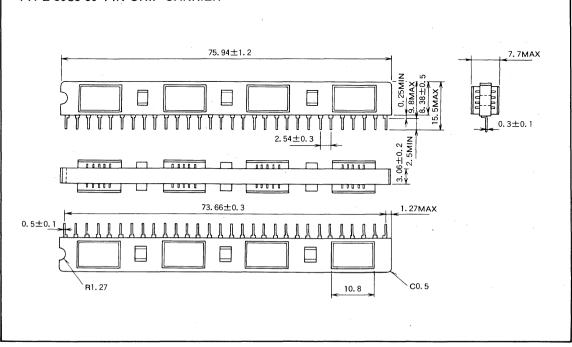

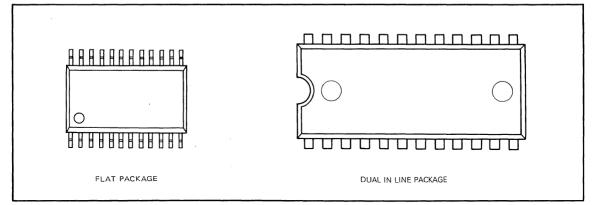

| Package Outlines                          |      |

| Letter Symbols for The Dynamic Parameters |      |

| Symbology                                 |      |

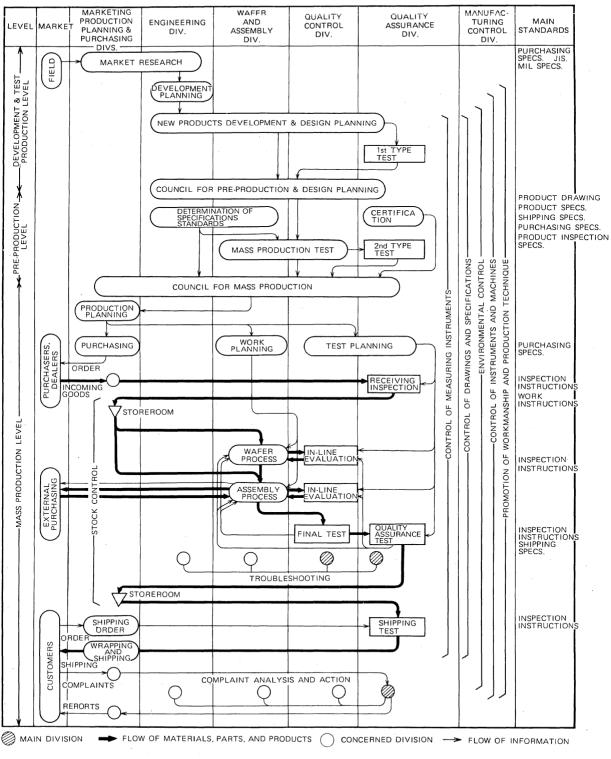

| Quality Assurance and Reliability Testing |      |

| Precautions in Handling MOS IC/LSIs       | 1—37 |

## **2** MOS DYNAMIC RAM

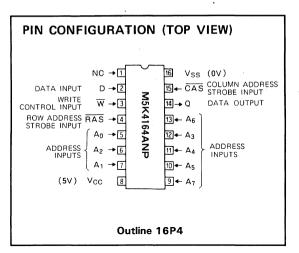

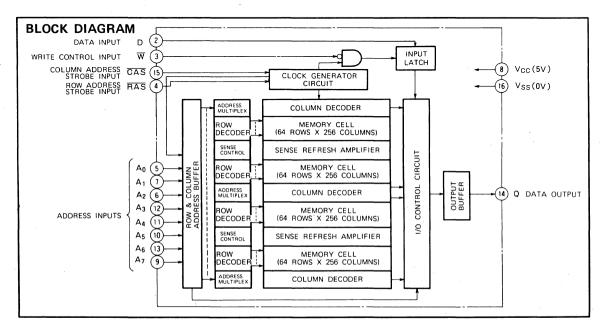

| M5K4164AP-12, -15     | 65536-Bit (65536-Word by 1-Bit) Dynamic RAM23            |

|-----------------------|----------------------------------------------------------|

| M5K4164ANP-12, -15    | 65536-Bit (65536-Word by 1-Bit) Dynamic RAM              |

| M5K4164ANP-20         | 65536-Bit (65536-Word by 1-Bit) Dynamic RAM2-24          |

| M5K4164AL-12, 15      | 65536-Bit (65536-Word by 1-Bit) Dynamic RAM234           |

| M5K4164ANL-12, -15    | 65536-Bit (65536-Word by 1-Bit) Dynamic RAM245           |

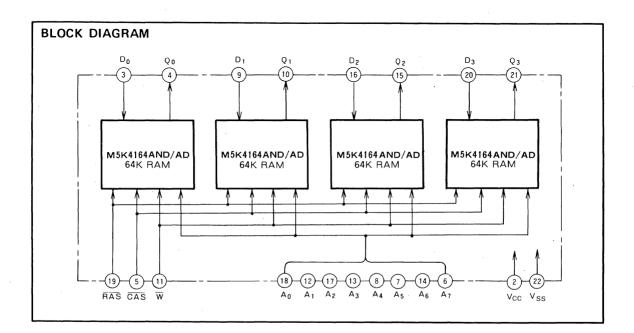

| M5K4164AND-12, -15    | 65536-Bit (65536-Word by 1-Bit) Dynamic RAM22            |

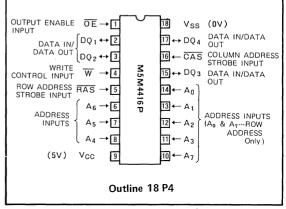

| M5M4416P-12, -15      | 65536-Bit (16384-Word by 4-Bit) Dynamic RAM              |

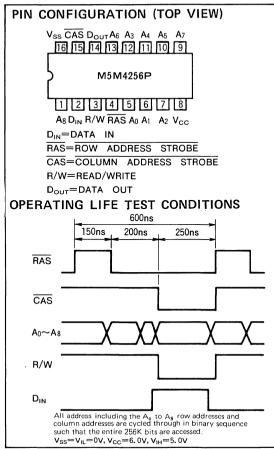

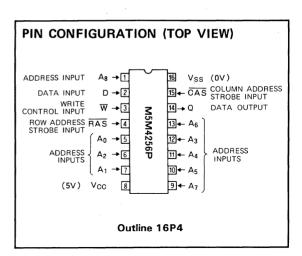

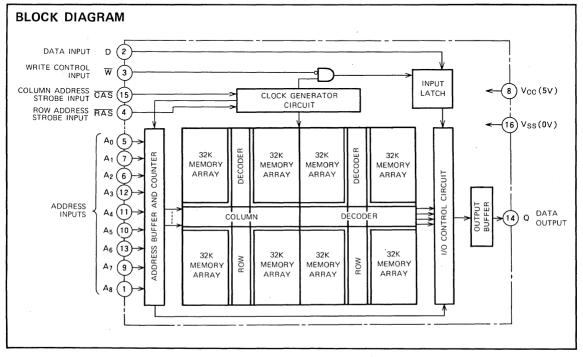

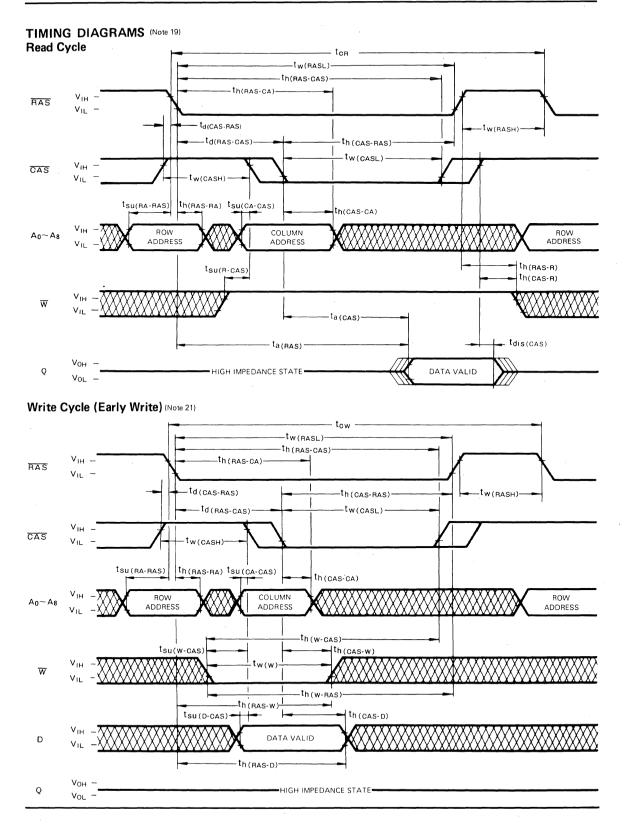

| M5M4256P-12, -15, -20 | 262144-Bit (262144-Word by 1-Bit) Dynamic RAM 2-80       |

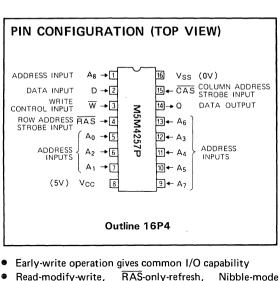

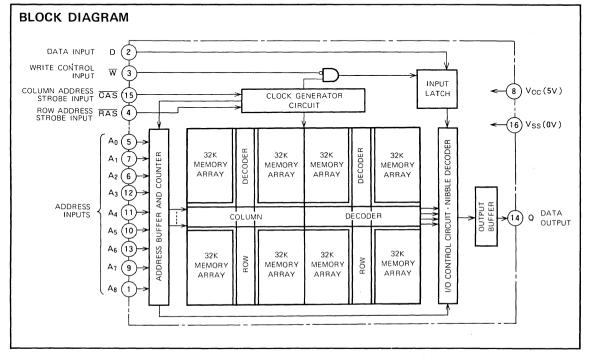

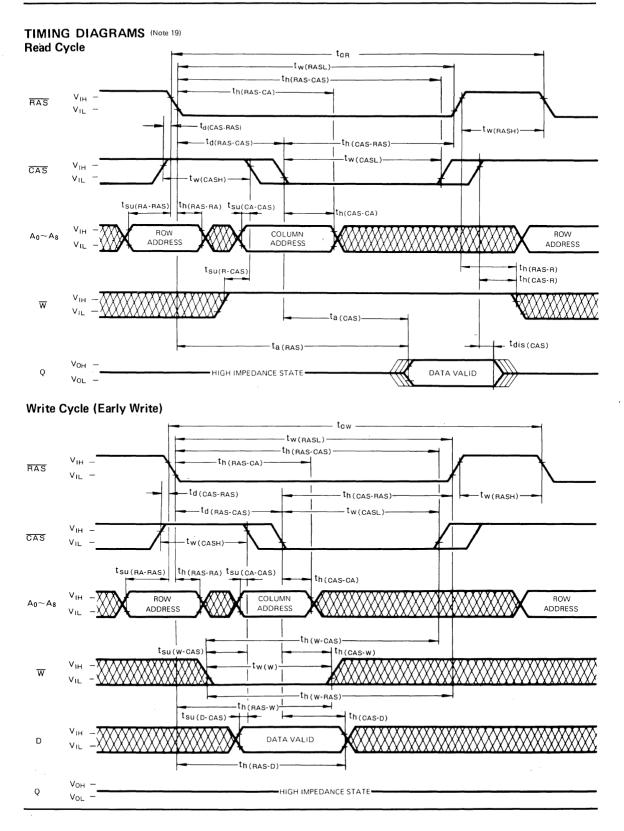

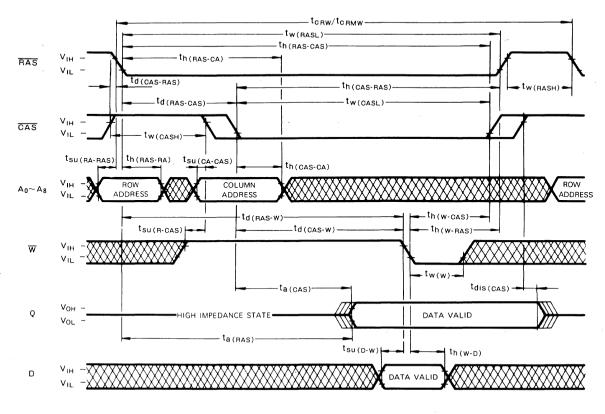

| M5M4257P-12, -15, -20 | 262144-Bit (262144-Word by 1-Bit) Dynamic RAM 2-95       |

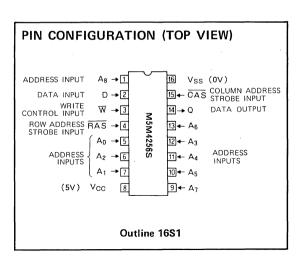

| M5M4256S-12, -15, -20 | 262144-Bit (262144-Word by 1-Bit) Dynamic RAM            |

| M5M4257S-12, -15, -20 | 262144-Bit (262144-Word by 1-Bit) Dynamic RAM            |

| M5M4256L-12, -15, -20 | 262144-Bit (262144-Word by 1-Bit) Dynamic RAM            |

| M5M4257L-12, -15, -20 | 262144-Bit (262144-Word by 1-Bit) Dynamic RAM2155        |

| M5M4464P-12, -15      | 262144-Bit (65536-Word by 4-Bit) Dynamic RAM······ 2-170 |

| MH6404AD1-15          | 262144-Bit (65536-Word by 4-Bit) Dynamic RAM             |

| MH6404AND1-15         | 262144-Bit (65536-Word by 4-Bit) Dynamic RAM             |

| MH6408AD-15           | 524288-Bit (65536-Word by 8-Bit) Dynamic RAM2-206        |

| MH6408AND-15          | 524288-Bit (65536-Word by 8-Bit) Dynamic RAM222222       |

# **3** NMOS STATIC RAM

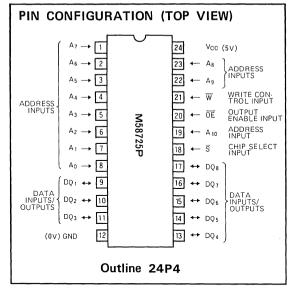

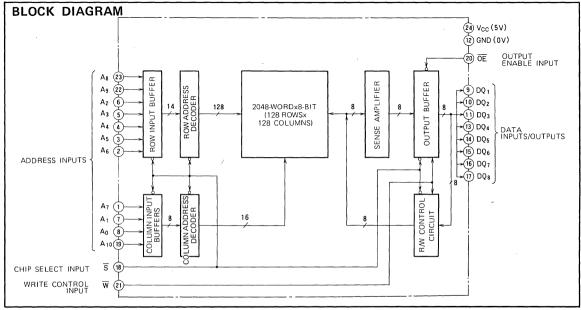

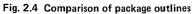

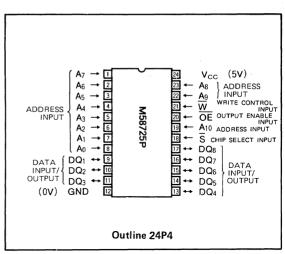

| M58725P, -15     | 16384-Bit (2048-Word by 8-Bit) Static RAM  |

|------------------|--------------------------------------------|

| M5M2167P-55, -70 | 16384-Bit (16384-Word by 1-Bit) Static RAM |

| M5M2168P-55, -70 | 16384-Bit (4096-Word by 4-Bit) Static RAM  |

## 4 CMOS STATIC RAM

| M5M5116P, -15         | 16384-Bit (2048-Word by 8-Bit) CMOS Static RAM······ 4-3 |

|-----------------------|----------------------------------------------------------|

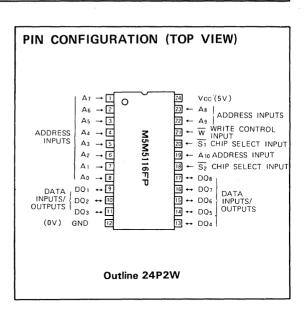

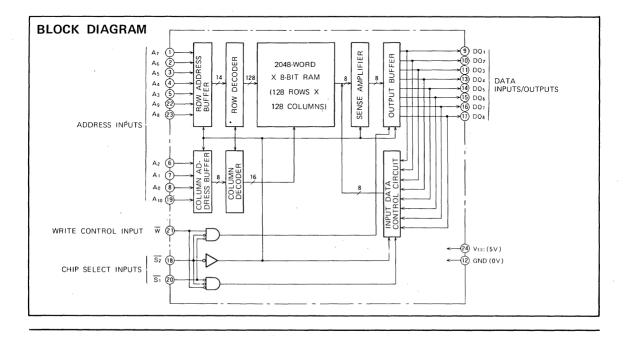

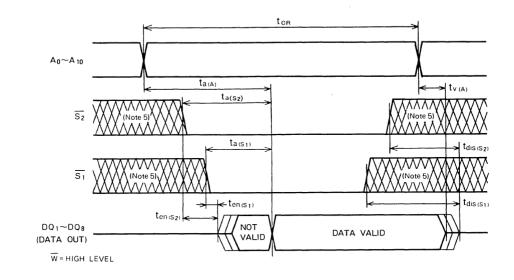

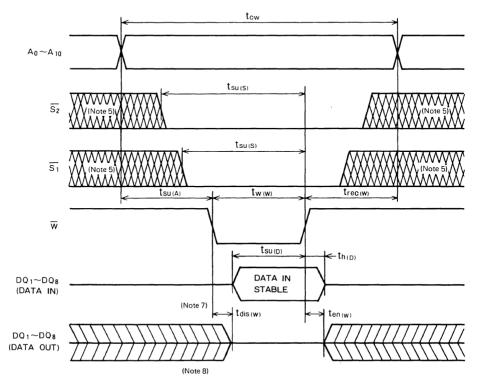

| M5M5116FP, -15        | 16384-Bit (2048-Word by 8-Bit) CMOS Static RAM·······4-8 |

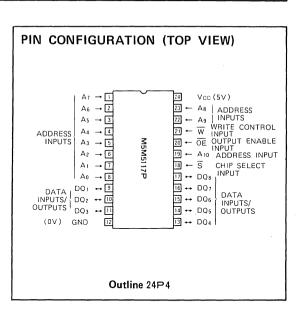

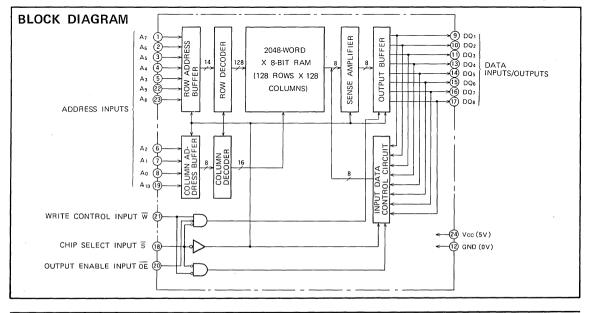

| M5M5117P, -15         | 16384-Bit (2048-Word by 8-Bit) CMOS Static RAM           |

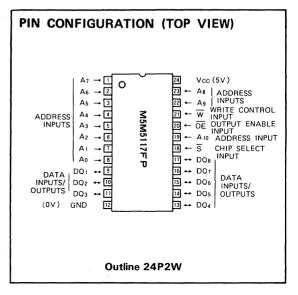

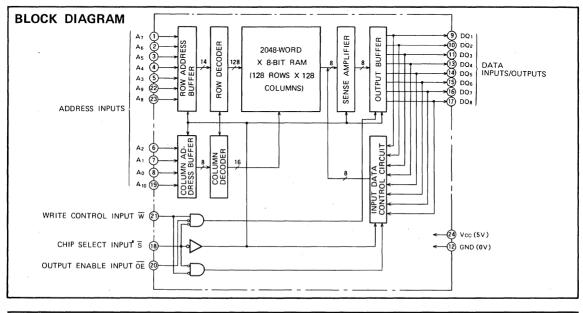

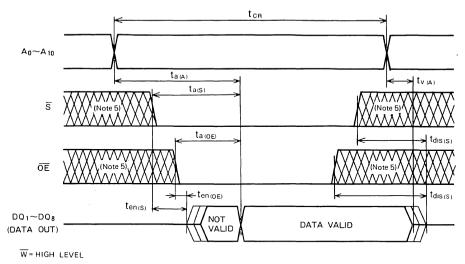

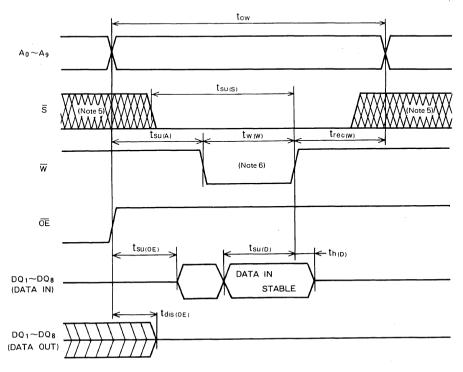

| M5M5117FP, -15        | 16384-Bit (2048-Word by 8-Bit) CMOS Static RAM 4-18      |

| M5M5118P, -15         | 16384-Bit (2048-Word by 8-Bit) CMOS Static RAM           |

| M5M5118FP, -15        | 16384-Bit (2048-Word by 8-Bit) CMOS Static RAM           |

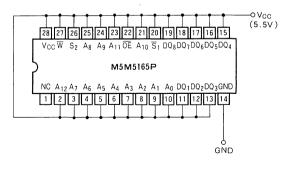

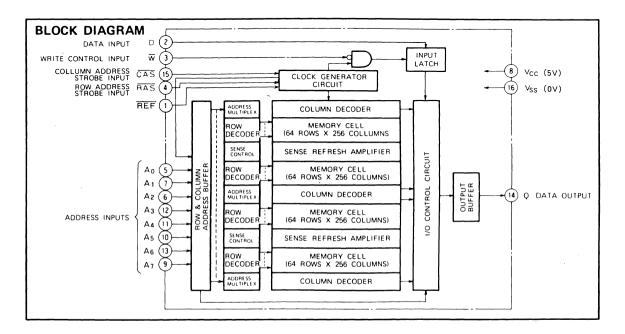

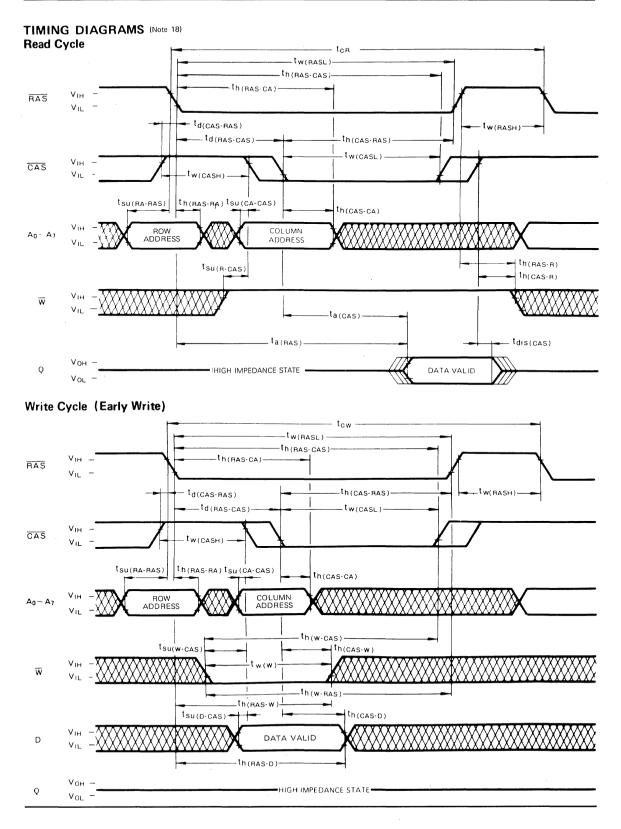

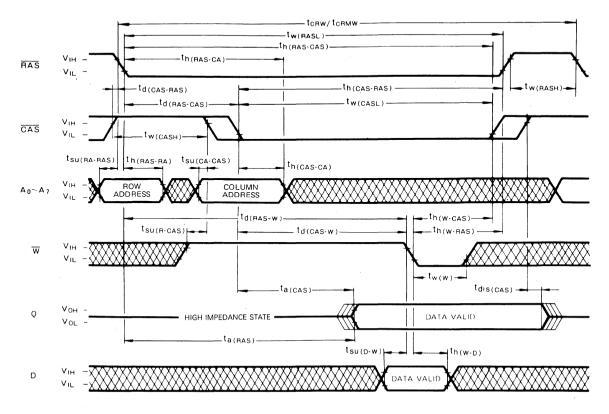

| M5M5165P-70, -10, -12 | , -15, -70L, -10L, -12L, -15L                            |

|                       | 65536-Bit (8192-Word by 8-Bit) CMOS Static RAM           |

Page

## 5 MOS MASK ROM

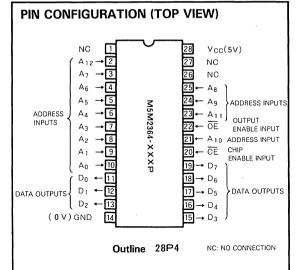

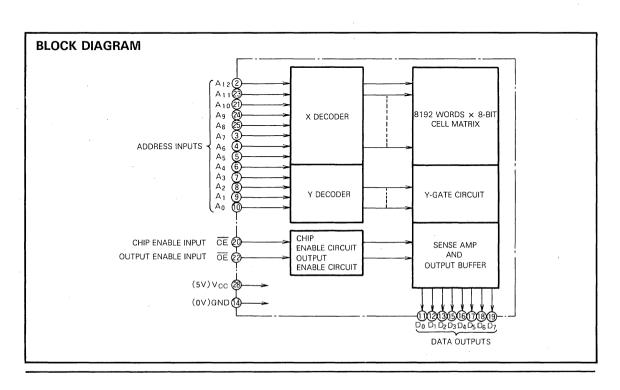

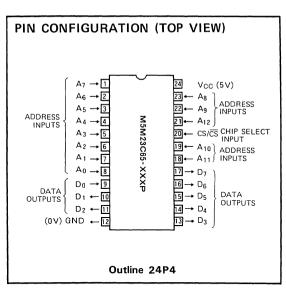

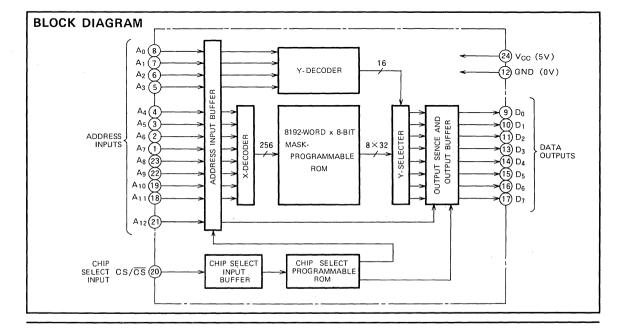

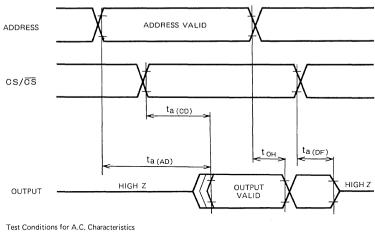

| M5M2364-XXXP   | 65536-Bit (8192-Word by 8-Bit) Mask-Programmable ROM5-3        |

|----------------|----------------------------------------------------------------|

| M5M2365-XXXP   | 65536-Bit (8192-Word by 8-Bit) Mask-Programmable ROM5-7        |

| M5M23C64-XXXP  | 65536-Bit (8192-Word by 8-Bit) Mask-Programmable ROM······5-10 |

| M5M23C65-XXXP  | 65536-Bit (8192-Word by 8-Bit) Mask-Programmable ROM5-13       |

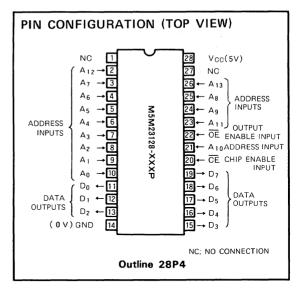

| M5M23128-XXXP  | 131072-Bit (16384-Word by 8-Bit) Mask-Programmable ROM516      |

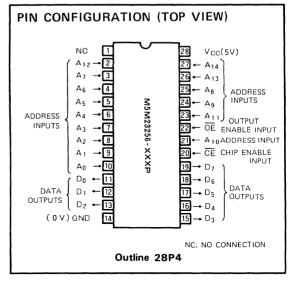

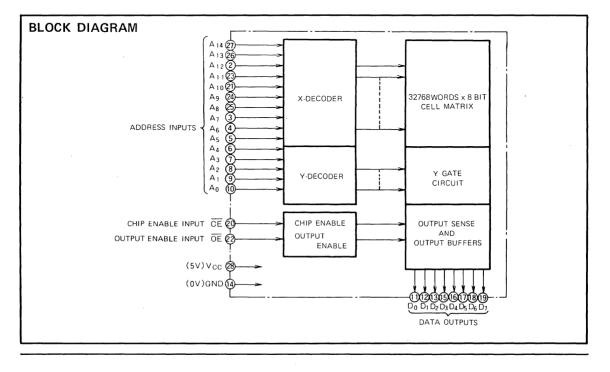

| M5M23256-XXXP  | 262144-Bit (32768-Word by 8-Bit) Mask-Programmable ROM5-19     |

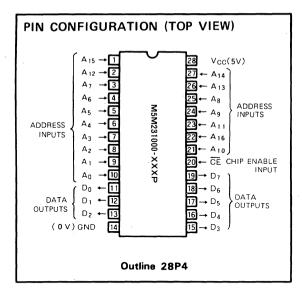

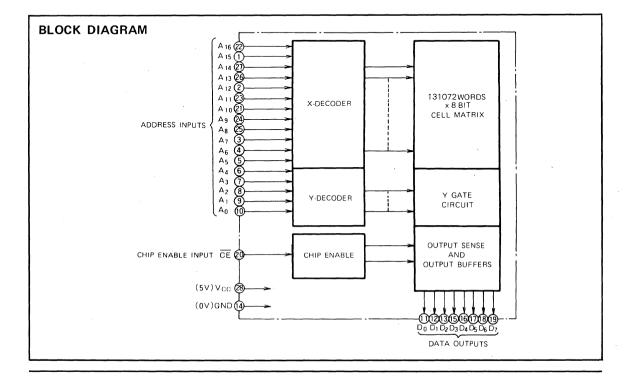

| M5M231000-XXXP | 1048576-Bit (131072-Word by 8-Bit) Mask-Programmable ROM5-22   |

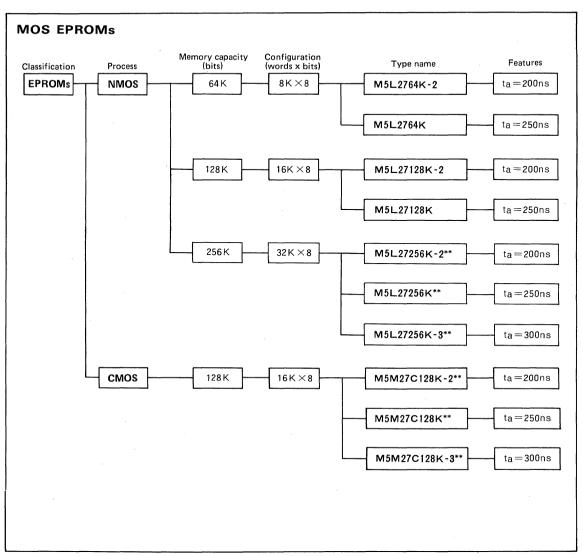

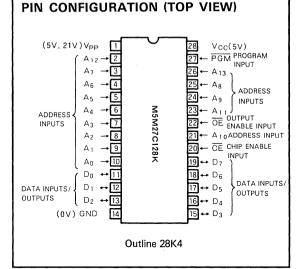

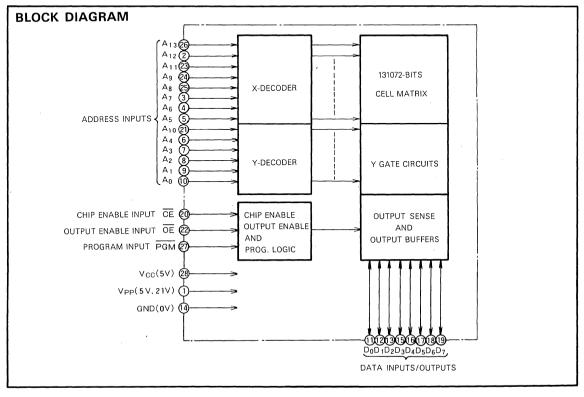

## 6 MOS EPROM

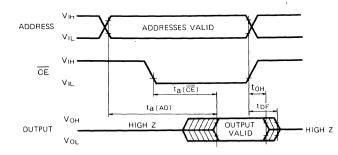

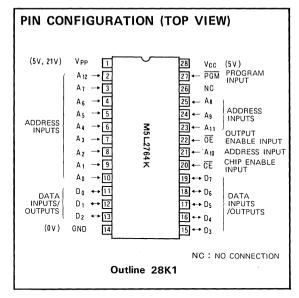

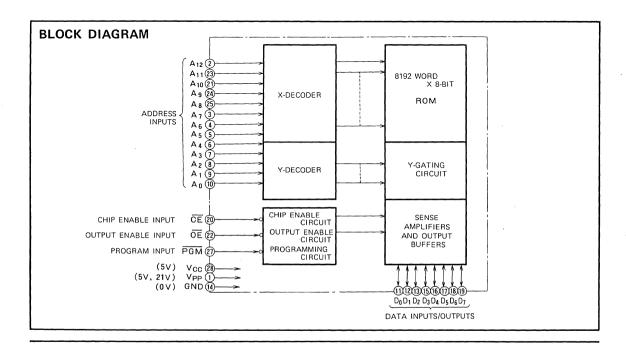

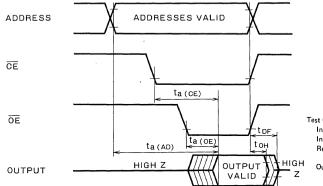

| M5L2764K, -2       | 65536-Bit (8192-Word by 8-Bit) Erasable and Electrically          |

|--------------------|-------------------------------------------------------------------|

|                    | Reprogrammable ROM······6—3                                       |

| M5L27128K, -2      | 131072-Bit (16384-Word by 8-Bit) Erasable and Electrically        |

|                    | Reprogrammable ROM······6—10                                      |

| M5M27C128K, -2, -3 | 3 131072-Bit (16384-Word by 8-Bit) CMOS Erasable and Electrically |

|                    | Reprogrammable ROM······6—19                                      |

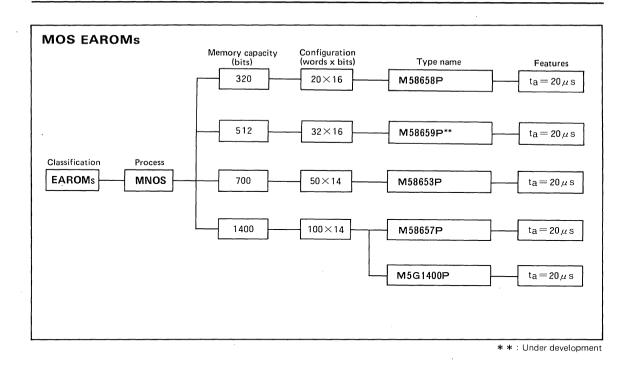

## **Z** MOS EAROM

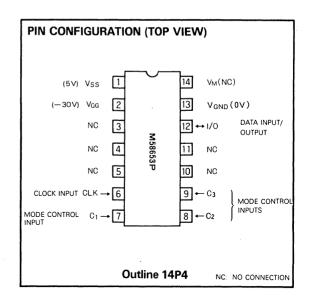

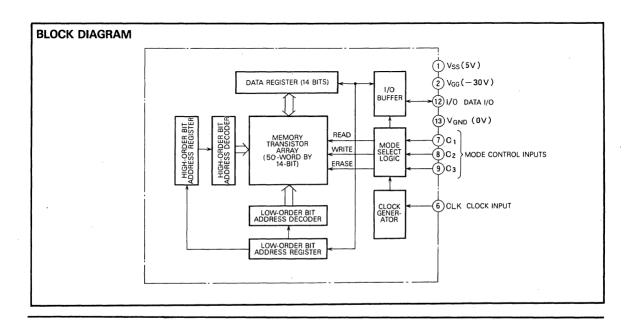

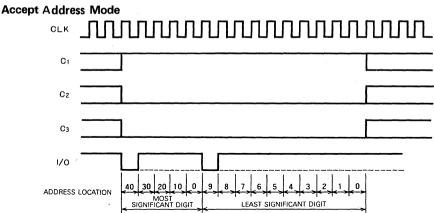

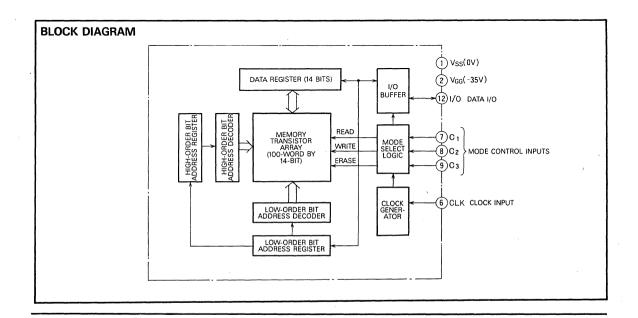

| M58653P  | 700-Bit (50-Word by 14-Bit) Electrically Alterable ROM          |

|----------|-----------------------------------------------------------------|

| M58657P  | 1400-Bit (100-Word by 14-Bit) Electrically Alterable ROM······· |

| M58658P  | 320-Bit (20-Word by 16-Bit) Electrically Alterable ROM7-15      |

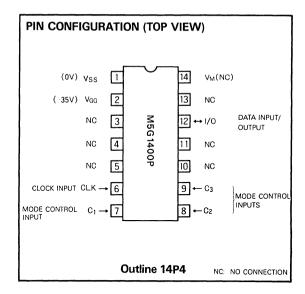

| M5G1400P | 1400-Bit (100-Word by 14-Bit) Electrically Alterable ROM        |

## 8 APPLICATIONS

| 64K-BIT DYNAMIC RAM |

|---------------------|

| STATIC RAM          |

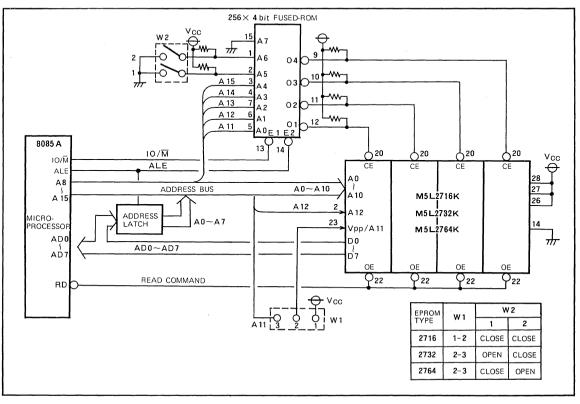

| EPROM8-51           |

**Contact Addresses for Further Information**

# GUIDANCE

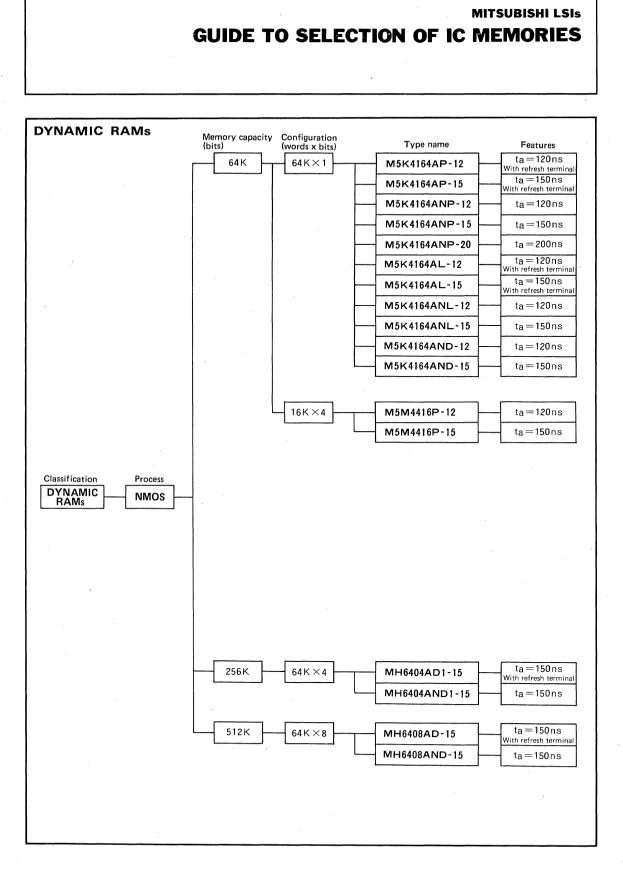

# GUIDE TO SELECTION OF IC MEMORIES

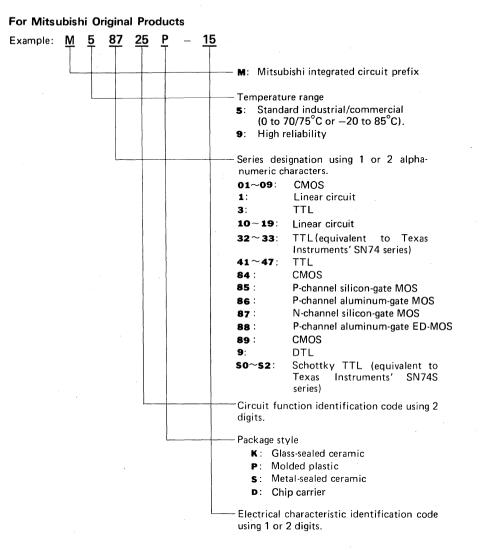

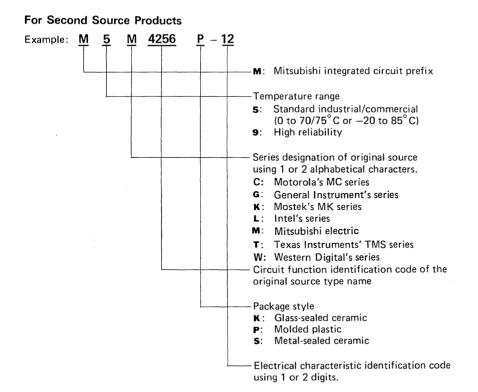

\* : New product \* \* : Under development

MITSUBISHI LSIS

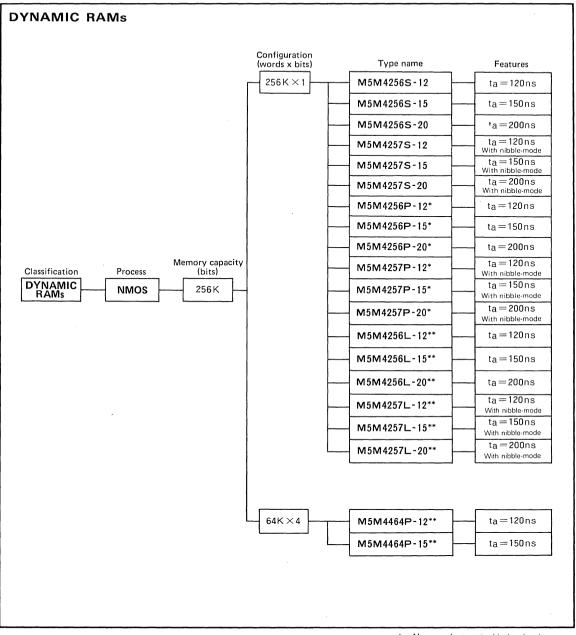

\* : New product \* \* : Under development

## **MITSUBISHI LSIs GUIDE TO SELECTION OF IC MEMORIES**

\* \*: Under development

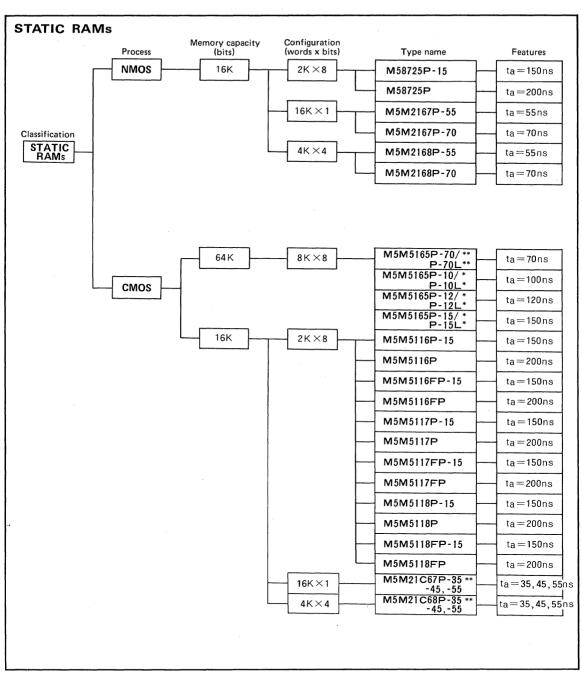

## MITSUBISHI LSIS GUIDE TO SELECTION OF IC MEMORIES

\* \* : Under development

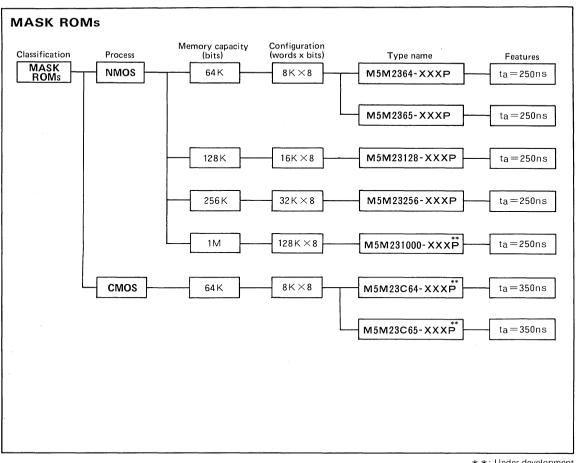

## MITSUBISHI LSIS GUIDE TO SELECTION OF IC MEMORIES

# MITSUBISHI LSIS

### ■64K-Bit DYNAMIC RAM

#### DIL

| Туре          | Structure | Memory<br>capacity<br>(configu-<br>ration) | Refresh<br>pin | Access<br>time<br>Max<br>(ns) | Cycle<br>time<br>Min<br>(ns) | Power<br>dis-<br>sipation<br>Typ<br>(mW) | Low power<br>dissipation<br>Max(mW)<br>Operating<br>time | Specifications | Package<br>outlines                                                                                                                | Inter-<br>changeable<br>products                                                                                      | Page     |      |     |                                                                            |                |                  |                                    |      |

|---------------|-----------|--------------------------------------------|----------------|-------------------------------|------------------------------|------------------------------------------|----------------------------------------------------------|----------------|------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|----------|------|-----|----------------------------------------------------------------------------|----------------|------------------|------------------------------------|------|

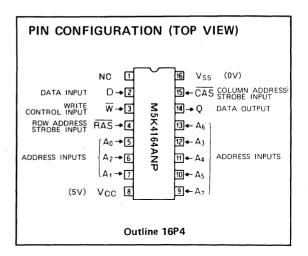

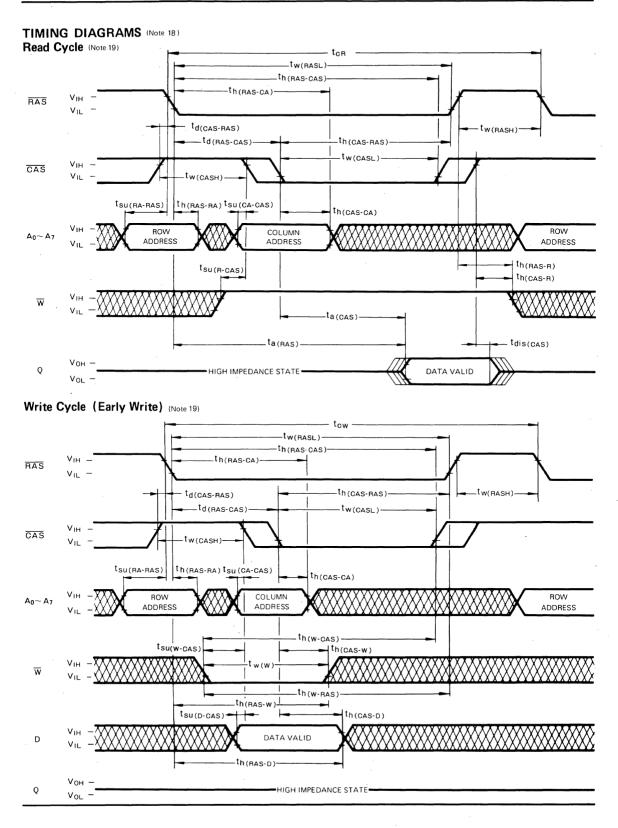

| M5K4164AP-12  |           | 64K<br>(64K×1)<br>64K<br>(16K×4)           |                |                               | Yes                          | 120                                      | 220                                                      | 175            | 275                                                                                                                                | <ul> <li>128 refresh cycles<br/>every 2 ms</li> <li>1-pin automatic and<br/>self-refreshing<br/>capability</li> </ul> | 16P4     | See  | 2—3 |                                                                            |                |                  |                                    |      |

| M5K4164AP-15  |           |                                            |                |                               | 150                          | 260                                      | 150                                                      | 250            | <ul> <li>CAS input allows<br/>hidden refresh, hidden<br/>automatic refresh,<br/>and hidden self-<br/>refresh operation.</li> </ul> | 16P4                                                                                                                  | page1-12 | 2—3  |     |                                                                            |                |                  |                                    |      |

| M5K4164ANP-12 | NMOS      |                                            |                | (64K×1)                       | (64K×1)                      |                                          | os                                                       |                |                                                                                                                                    | 120                                                                                                                   | 220      | 175  | 275 | ● 128 refresh cycles<br>every 2ms.<br>● CAS input allows<br>hidden refresh |                | See<br>page 1-12 |                                    |      |

| M5K4164ANP-15 |           |                                            |                |                               |                              |                                          |                                                          |                | No                                                                                                                                 | No                                                                                                                    | 150      | 260  | 150 | 250                                                                        | operation 16P4 |                  | 2—14                               |      |

| M5K4164ANP-20 |           |                                            |                |                               | 200                          | 330                                      | 125                                                      | 225            |                                                                                                                                    |                                                                                                                       |          | 2—24 |     |                                                                            |                |                  |                                    |      |

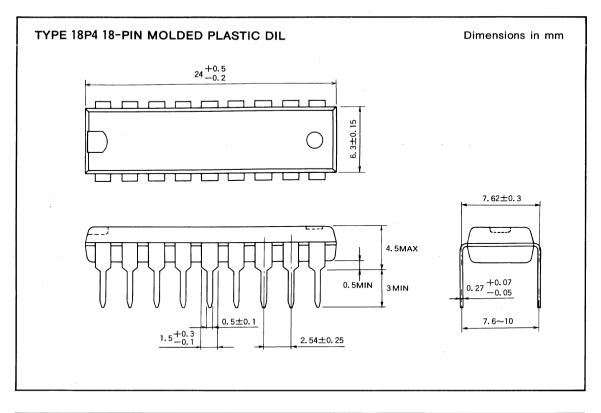

| M5M4416P-12   |           |                                            |                |                               | 120                          | 220                                      | 175                                                      | 275            | • 128 refresh cycles                                                                                                               | 1054                                                                                                                  |          | 2-65 |     |                                                                            |                |                  |                                    |      |

| M5M4416P-15   |           |                                            |                | (16K×4)                       | (16K×4)                      | (16K×4)                                  | (16K×4)                                                  | (16K×4)        | (16K×4)                                                                                                                            | (16K×4)                                                                                                               | (16K×4)  | <×4) | 150 | 260                                                                        | 150            | 250              | every 2ms<br>• 4-bit configuration | 18P4 |

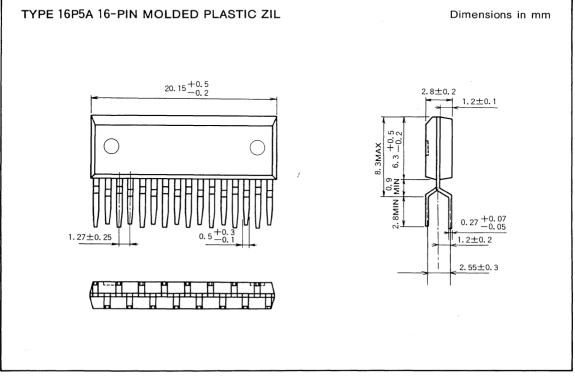

### ZIL ,

| Туре          | Structure | Memory<br>capacity<br>(configu-<br>ration | Refresh<br>pin | Access<br>time<br>Max(ns) | Specifications                                                                                                                    | Package<br>outlines | Inter-<br>changeable<br>products | Page |

|---------------|-----------|-------------------------------------------|----------------|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------|---------------------|----------------------------------|------|

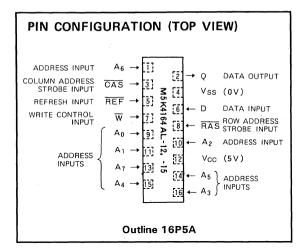

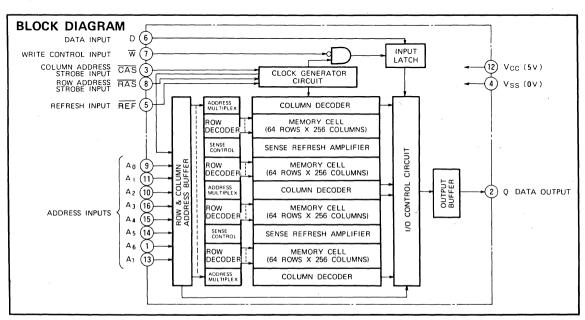

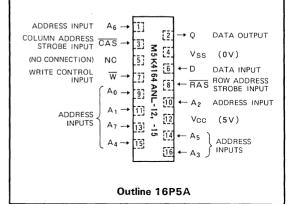

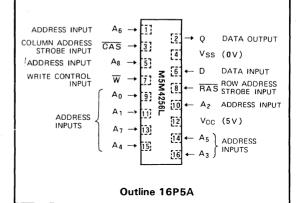

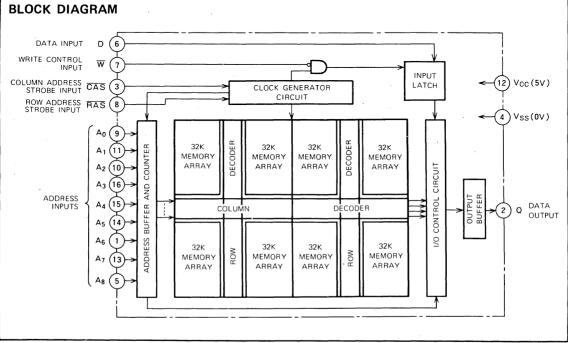

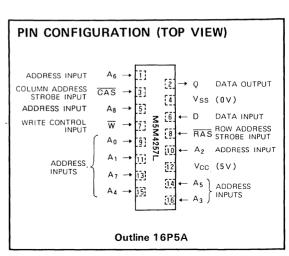

| M5K4164AL-12  |           |                                           | Yes            | 120                       | <ul> <li>Same electrical characteristics as the<br/>M5K4164AP and ANP series.</li> <li>Package 16pin zig zag in-line</li> </ul>   | —16P5A              | _                                | 2—34 |

| M5K4164AL-15  | NMOS      | 64K                                       | 165            | 150                       | <ul> <li>5-pin automatic and self-refresh<br/>capability</li> </ul>                                                               |                     |                                  |      |

| M5K4164ANL-12 |           | (64K×1)                                   | No             | 120                       | <ul> <li>Same electrical characteristics as the<br/>M5K4164AP and ANP series.</li> <li>Package: 16-pin zig-zag in-line</li> </ul> |                     |                                  | 2-45 |

| M5K4164ANL-15 |           |                                           | INU            | 150                       |                                                                                                                                   |                     |                                  |      |

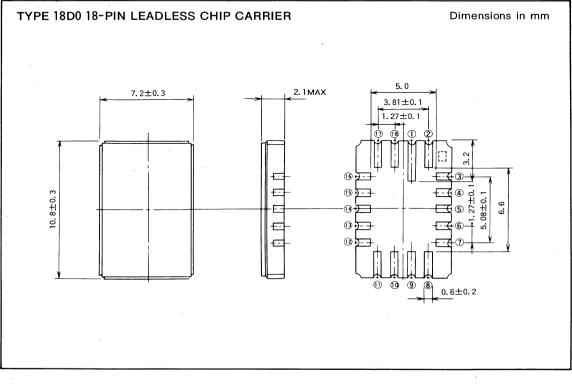

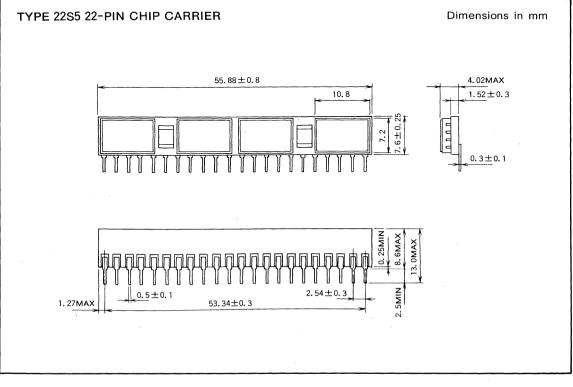

#### Chip carrier

| Туре          | Structure | Memory<br>capacity<br>(configu-<br>ration) | Refresh<br>pin | Access<br>time<br>Max(ns) | Specifications                                                                                                                         | Package<br>outlines | Inter-<br>changeable<br>products | Page |

|---------------|-----------|--------------------------------------------|----------------|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------|---------------------|----------------------------------|------|

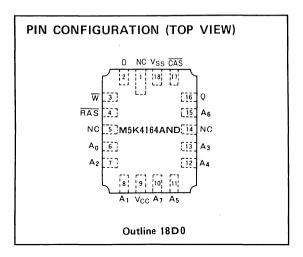

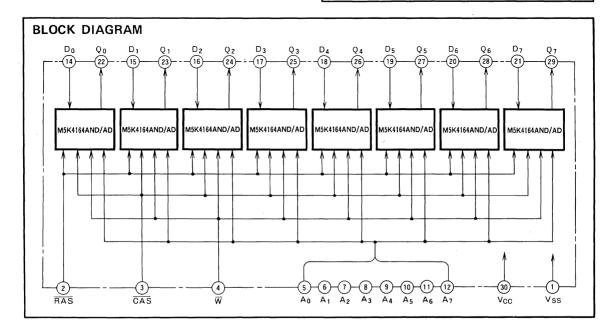

| M5K4164AND-12 | NMOS      | 64K                                        | No             | 120                       | <ul> <li>Same electrical characteristics as the<br/>M5K4164AP and ANP series</li> <li>Package: 18-pin of which two are open</li> </ul> | 1000                | See                              | 0 55 |

| M5K4164AND-15 |           | (64K×1)                                    |                | 150                       | ●Lead pitch: 1.27mm<br>●External dimensions: 7.2×10.8×1.9mm                                                                            | 18D0                | page <b>1-12</b>                 | 2—55 |

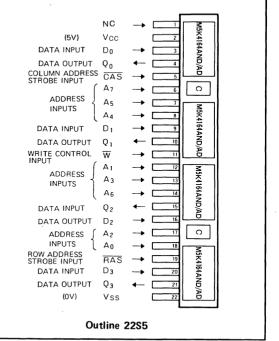

#### SIL MODULE

| Туре          | Structure | Memory<br>capacity<br>(configu-<br>ration) | Refresh<br>pin | Access<br>time<br>Max(ns) | Number<br>of chip<br>carrier | Specifications                                                                                             | Package<br>outlines | Inter-<br>changeable<br>products | Page  |

|---------------|-----------|--------------------------------------------|----------------|---------------------------|------------------------------|------------------------------------------------------------------------------------------------------------|---------------------|----------------------------------|-------|

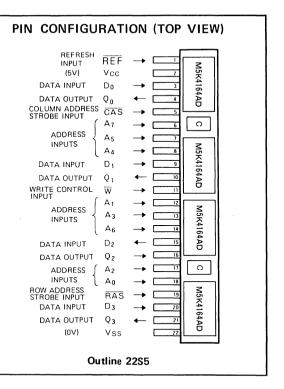

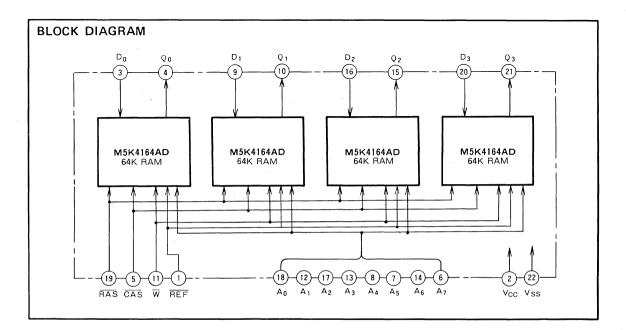

| MH6404AD1-15  |           | 256K<br>(64K×4)                            | Yes            | - 150 -                   | Four units<br>(64K×4-bit)    | <ul> <li>Package: 22-pin SIL<br/>configuration</li> <li>External measurements:<br/>7.6×56×3.5mm</li> </ul> | 2255                |                                  | 2—185 |

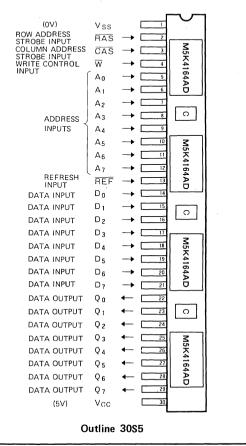

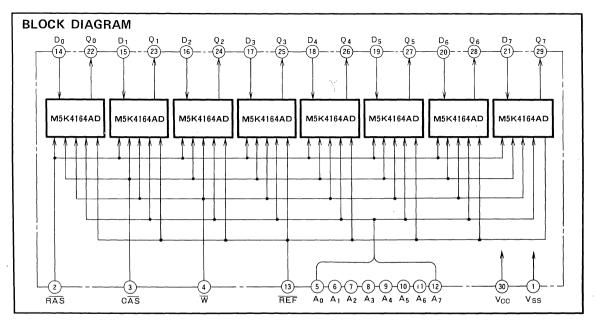

| MH6408AD-15   | NMOS      | 512K<br>(64K×8)                            |                |                           | Eight units<br>(64K×8-bit)   | <ul> <li>Package: 30-pin SIL<br/>configuration</li> <li>External measurements:<br/>8.4×76×7mm</li> </ul>   | 3055                |                                  | 2—206 |

| MH6404AND1-15 |           | 256 K<br>(64K×4)                           | No             |                           | Four units<br>(64K×4-bit)    | <ul> <li>Package: 22-pin SIL<br/>configuration</li> <li>External measurements:<br/>7.6×56×3.5mm</li> </ul> | 2255                |                                  | 2—196 |

| MH6408AND-15  |           | 512K<br>(64K×8)                            | UVI            |                           | Eight units<br>(64K×8-bit)   | <ul> <li>Package: 30-pin<br/>configuration</li> <li>External measurements:<br/>8.4×76×7mm</li> </ul>       | 30\$5               | _                                | 2—217 |

### ■256K-Bit DYNAMIC RAM

DIL

| Туре           | Structure | Memory<br>capacity<br>(configu-<br>ration) | Function<br>mode | Access<br>time<br>Max(ns) | Cycle<br>time<br>Min(ns) | Power<br>dissipation<br>Typ<br>(mW) | Low power<br>dissipation<br>Max(mW)<br>Operating time                                                              | Specifications                                                             | Package<br>outlines | Inter-<br>changeable<br>products | Page  |

|----------------|-----------|--------------------------------------------|------------------|---------------------------|--------------------------|-------------------------------------|--------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|---------------------|----------------------------------|-------|

| M5M4256P-12*   |           |                                            |                  | 100                       |                          |                                     | 360                                                                                                                | ●256 refresh cycles<br>every 4ms<br>●CAS before BAS                        | 16P4                |                                  | 2—80  |

| M5M4256S-12    |           |                                            |                  | 120                       | 230                      | 260                                 | 413                                                                                                                | ecAS before RAS<br>refresh operation<br>capability<br>CAS input allows     | 1651                |                                  | 2—110 |

| M5M4256P-15*   |           |                                            | mode             | 150                       | 200                      |                                     | 330                                                                                                                | hidden refresh<br>operation.                                               | 16P4                |                                  | 2—80  |

| M5M4256S-15    |           |                                            | Page I           | 150                       | 260                      | 230                                 | 385                                                                                                                |                                                                            | 16S1                |                                  | 2—110 |

| M5M4256P-20*   |           | 256K                                       |                  | 200                       | 222                      | 100                                 | 275                                                                                                                |                                                                            | 16P4                | Coo                              | 2—80  |

| M5M4256S-20    |           | 256K<br>(256K × 1)                         |                  | 200                       | 330                      | 190                                 | 303                                                                                                                |                                                                            | 16S1                | See<br>page1-12                  | 2—110 |

| M5M4257P-12*   |           | 256K<br>(256K×1)                           |                  |                           |                          | 260                                 | 360                                                                                                                | ●256 refresh cycles<br>every 4ms.<br>●CAS before RAS                       | 16P4                | 2—95                             |       |

| M5M4257S-12    | NMOS      |                                            | mode             | 120                       | 230                      | 260                                 | 413                                                                                                                | •CAS before HAS<br>refresh operation<br>capability.<br>•CAS input allows   | 1651                |                                  | 2—125 |

| M5M4257P-15*   |           |                                            |                  | 450                       | 260                      |                                     | 330                                                                                                                | hidden refresh<br>operation                                                | 16P4                | 16P4                             | 2—95  |

| M5M4257S-15    |           |                                            | Nibble mode      | 150                       | 260                      | 230                                 | 385                                                                                                                | -                                                                          | 1651                |                                  | 2—125 |

| M5M4257P-20*   |           |                                            | 2                | 200                       | 330                      | 100                                 | 275                                                                                                                |                                                                            | 16P4                |                                  | 2—95  |

| M5M4257S-20    |           |                                            |                  | 200                       | 330                      | 190                                 | 303                                                                                                                |                                                                            | 16S1                |                                  | 2—125 |

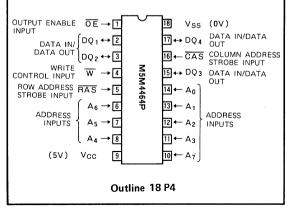

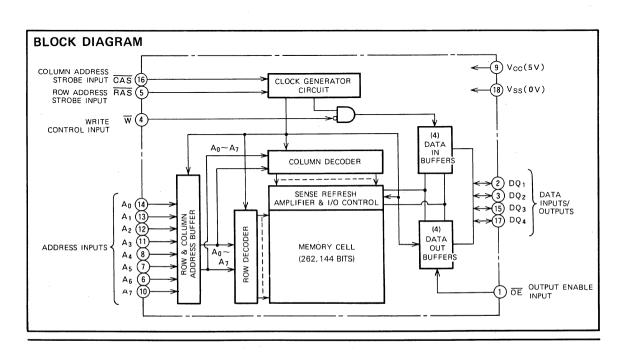

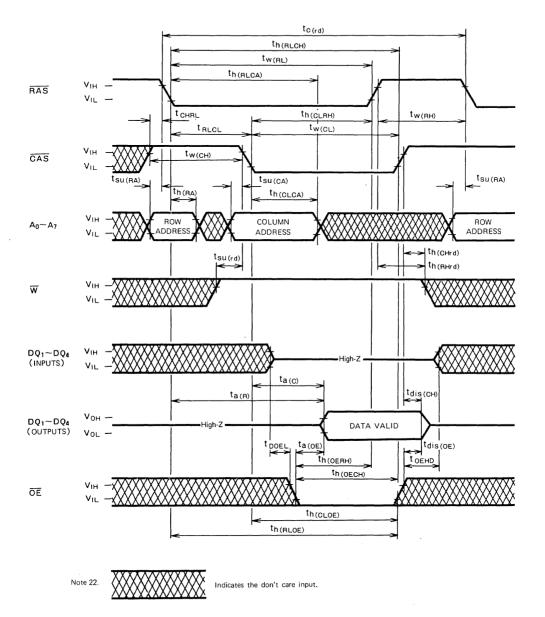

| M5M4464P-12**  |           | 256 K                                      | mode             | 120                       | 230 260                  | 360                                 | <ul> <li>256 refresh cycles<br/>every 4ms.</li> <li>CAS before RAS<br/>refresh operation<br/>capability</li> </ul> | 18P4                                                                       |                     | 2-170                            |       |

| M5 M4464P-15** |           | 256K<br>(64K×4)                            | Page             | 150                       | 260                      | 230                                 | 330                                                                                                                | •CAS input allows<br>hidden refresh ope-<br>ration<br>•4-bit configuration | 1824                |                                  | 2 170 |

\* : New product • \*\* : Under development

.

# MITSUBISHI LSIS

ZIL

| Туре          | Structure | Memory<br>capacity<br>(configu-<br>ration) | Function<br>mode | Access<br>time<br>Max(ns) | Cycle<br>time<br>Min(ns) | Power<br>dissipation<br>Typ<br>(mW) | Low power<br>dissipation<br>Max(mW)<br>Operating time | Specifications                         | Package<br>outlines | inter-<br>changeable<br>products | Page     |          |          |  |  |  |            |     |     |     |     |                                    |

|---------------|-----------|--------------------------------------------|------------------|---------------------------|--------------------------|-------------------------------------|-------------------------------------------------------|----------------------------------------|---------------------|----------------------------------|----------|----------|----------|--|--|--|------------|-----|-----|-----|-----|------------------------------------|

| M5M4256L-12** |           |                                            | 0.0              | 120                       | 230                      | 260                                 | 360                                                   | Same electrical                        |                     |                                  |          |          |          |  |  |  |            |     |     |     |     |                                    |

| M5M4256L-15** |           | 256K                                       | Page<br>mode     | 150                       | 260                      | 230                                 | 330                                                   | characteristics as<br>the M5M4256P and |                     |                                  | 2—140    |          |          |  |  |  |            |     |     |     |     |                                    |

| M5M4256L-20** | NMOS      |                                            | 256 K            | 256 K                     | αE                       | 200                                 | 330                                                   | 190                                    | 275                 | M5M4257P series.                 |          |          |          |  |  |  |            |     |     |     |     |                                    |

| M5M4257L-12** | NIVIO5    |                                            |                  |                           | (256K×1)                 | (256K×1)                            | (256K×1)                                              | (256K×1)                               | (256K×1)            | (256K×1)                         | (256K×1) | (256K×1) | (256K×1) |  |  |  | <u>e</u> e | 120 | 230 | 260 | 360 | Package 16-pin<br>zig-zag in line. |

| M5M4257L-15** |           |                                            |                  |                           | 260                      | 230                                 | 330                                                   | ziy-zay in line.                       |                     |                                  | 2        |          |          |  |  |  |            |     |     |     |     |                                    |

| M5M4257L-20** |           | Nibt                                       |                  | 200                       | 330                      | 190                                 | 275                                                   | 1                                      |                     |                                  |          |          |          |  |  |  |            |     |     |     |     |                                    |

### ■16K-Bit STATIC RAM

| Туре           | Structure | Memory<br>capacity | Memory<br>configuration<br>(Word×Bit) | Supply<br>voltage<br>(V) | Typical<br>power<br>dissipation<br>Typ(mW) | Access<br>time<br>Max(ns) | Cycle<br>time<br>Min(ns) | Package<br>outlines | Inter-<br>changeable<br>products | Page |

|----------------|-----------|--------------------|---------------------------------------|--------------------------|--------------------------------------------|---------------------------|--------------------------|---------------------|----------------------------------|------|

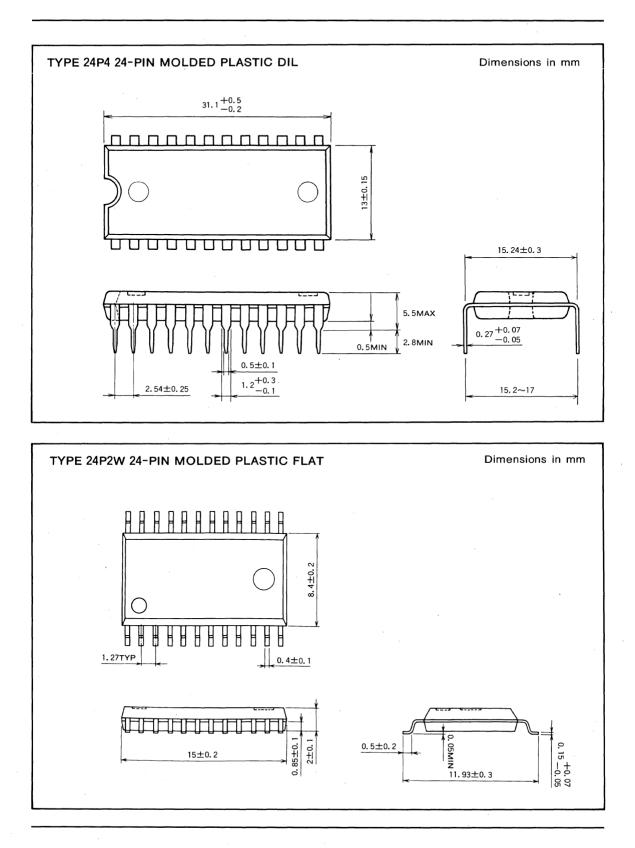

| M58725P-15     |           |                    | 2K×8                                  |                          | 250                                        | 150                       | 150                      | 24.04               |                                  | 3—3  |

| M58725P        |           |                    | 21/~0                                 |                          | 250                                        | 200                       | 200                      | 24P4                | See                              | 3-3  |

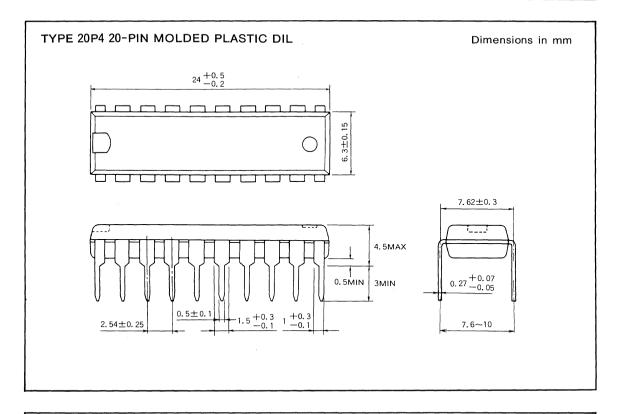

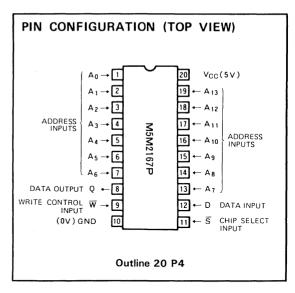

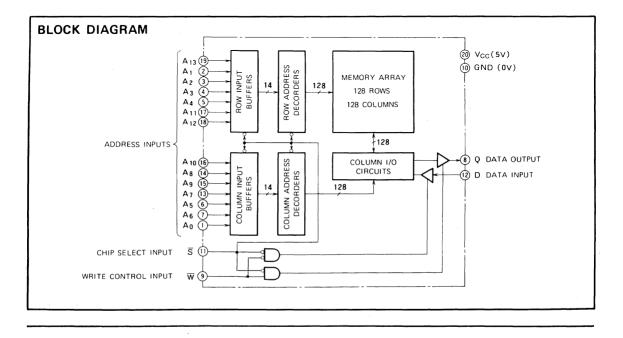

| M5M2167P-55    | NMOS      |                    | 16K×1                                 |                          | 400                                        | 55                        | 55                       | 20P4                | page1-14                         | 3—9  |

| M5M2167P-70    | 111000    |                    | TURXT                                 |                          | 400                                        | 70                        | 70                       | 201-4               | pager 14                         | 5 5  |

| M5M2168P-55    |           |                    | 4K×4                                  |                          | 500                                        | 55                        | 55                       | 20P4                |                                  | 3—13 |

| M5M2168P-70    |           |                    | 41(7,4                                |                          | 500                                        | 70                        | 70                       | 201-4               |                                  | 5 15 |

| M5M5116P-15    |           |                    |                                       |                          |                                            | 150                       | 150                      | 24P4                | See                              | 4-3  |

| M5M5116P       |           |                    |                                       |                          |                                            | 200                       | 200                      | 24174               | page1-14                         | 4 3  |

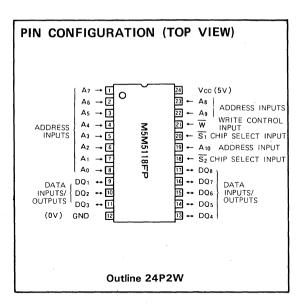

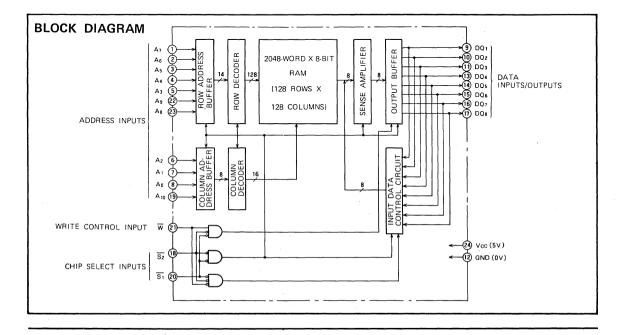

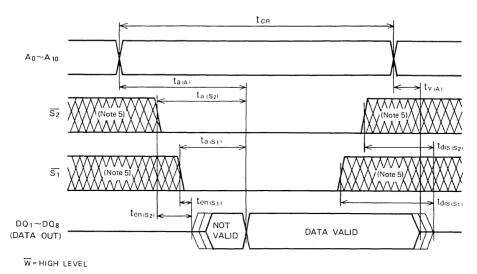

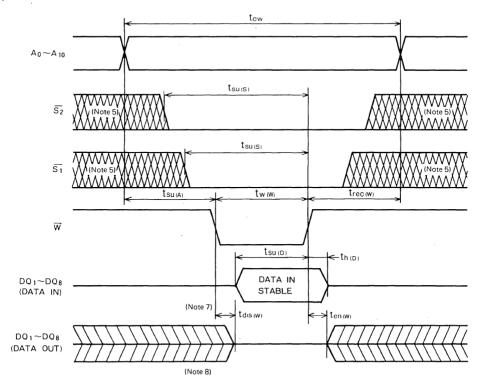

| M5M5116FP-15   |           | 16K                |                                       |                          | % 150                                      | 150                       | 150                      | 24P2W               | _                                | 4—8  |

| M5M5116FP      |           |                    |                                       | 5±10%                    |                                            | 200                       | 200                      | 2472 1              |                                  | 4-0  |

| M5M5117P-15    |           |                    |                                       |                          |                                            | 150                       | 150                      | 24 P4               | , See                            | 4-13 |

| M5M5117P       |           |                    | 2K×8                                  |                          |                                            | 200                       | 200                      | 24174               |                                  | 413  |

| M5M5117FP-15   |           |                    | LIXXO                                 |                          |                                            | 150                       | 150                      | 24P2W               |                                  | 4-18 |

| M5M5117FP      |           |                    |                                       |                          |                                            | 200                       | 200                      | 24-2 1              | page1-14                         | 4,10 |

| M5M5118P-15    | смоз      |                    |                                       |                          |                                            | 150                       | 150                      | 24P4                |                                  | 4-23 |

| M5M5118P       |           |                    |                                       |                          |                                            | 200                       | 200                      | 24174               |                                  | 4 23 |

| M5M5118FP-15   |           |                    |                                       |                          |                                            | 150                       | 150                      | 24P2W               |                                  | 4-28 |

| M5M5118FP      |           |                    |                                       |                          |                                            | 200                       | 200                      | 24 - 2 11           |                                  | 4 20 |

| M5M21C67P-35** |           |                    | ſ                                     |                          |                                            | 35                        | 35                       |                     |                                  |      |

| M5M21C67P-45** |           |                    | 16K×1                                 |                          |                                            | 45                        | 45                       | 20P4                |                                  | -    |

| M5M21C67P-55** |           |                    |                                       |                          | 200                                        | 55                        | 55                       |                     |                                  |      |

| M5M21C68P-35** |           |                    |                                       |                          | 200                                        | 35                        | 35                       |                     |                                  |      |

| M5M21C68P-45** |           |                    | 4K×4                                  |                          |                                            | 45                        | 45                       | 20P4                | P4                               | -    |

| M5M21C68P-55** |           |                    |                                       |                          |                                            | 55                        | 55                       |                     |                                  |      |

#### ■64K-Bit STATIC RAM

|                |           |                    | Memory        | Supply       | Power d   | issipation | Access  | Cycle   | age<br>nes | Inter-     |      |

|----------------|-----------|--------------------|---------------|--------------|-----------|------------|---------|---------|------------|------------|------|

| Туре           | Structure | Memory<br>capacity | configuration | voltage      | Operating | Standby    | time    | time    | Packa      | changeable | Page |

|                |           |                    | (Word×Bit)    | ( <b>v</b> ) | Typ(mW)   | Max(mW)    | Max(ns) | Max(ns) | Pa         | products   |      |

| M5M5165P-70**  |           |                    |               |              |           |            | 70      | 70      |            |            |      |

| M5M5165P-10*   |           |                    |               |              |           | 11         | 100     | 100     |            | 0          |      |

| M5M5165P-12*   |           |                    |               | 5±10%        |           | 11         | 120     | 120     |            | See        |      |

| M5M5165P-15*   | смоз      | 64K                | 8K×8          |              | 150       |            | 150     | 150     |            | page1-14   |      |

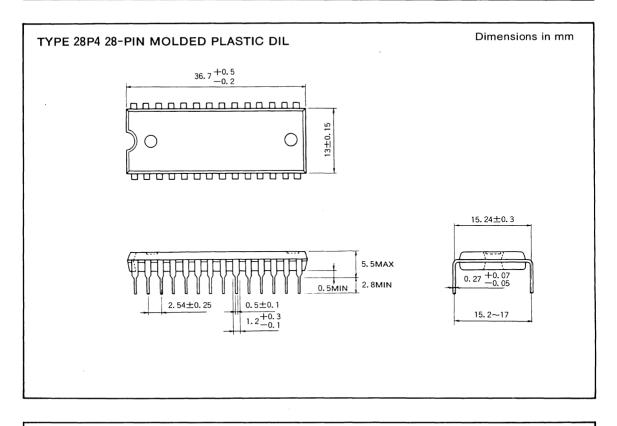

| M5M5165P-70L** | 01103     | 041                | 01 ~ 0        | 5±10%        | 150       |            | 70      | 70      | 28P4       |            | 4—33 |

| M5M5165P-10L*  |           |                    |               |              |           | 0.55       | 100     | 100 ·   |            | -          |      |

| M5M5165P-12L*  |           |                    |               |              |           | 0.55       | 120     | 120     |            | See        |      |

| M5M5165P-15L*  |           |                    |               |              |           |            | 150     | 150     |            | page1-14   |      |

\*: New product \*\*: Under development

#### MASK ROM

| Туре .           | Structure | Memory<br>capacity | Memory<br>configuration<br>(Word×Bit) | Supply<br>voltage<br>(V) | Typical<br>power<br>dissipation<br><b>Typ(mW)</b> | Access<br>time<br>Max(ns) | Cycle<br>time<br>Min(ns) | Package<br>outlines | Inter-<br>changeable<br>products | Page |

|------------------|-----------|--------------------|---------------------------------------|--------------------------|---------------------------------------------------|---------------------------|--------------------------|---------------------|----------------------------------|------|

| M5M2364-XXXP     |           | 64K                | 8K×8                                  |                          | 200                                               | 250                       |                          | 28P4                | MK37000                          | 5-3  |

| M5M2365-XXXP     | 1         | 04K                |                                       |                          | 150                                               |                           | _                        | 24P4                | MK36000                          | 5-7  |

| M5M23128-XXXP    | NMOS      | 128K               | 16K×8                                 |                          | 200                                               | 250                       | -                        |                     | μPD23128                         | 5-16 |

| M5M23256-XXXP    | 1         | 256K               | 32K×8                                 | 5±10%                    |                                                   |                           | _                        | 28P4                | MK38000                          | 5-19 |

| M5M231000-XXXP** |           | 1M                 | 128K×8                                | 5±1070                   |                                                   |                           | -                        | 281-4               |                                  | 522  |

| M5M23C64-XXXP**  | смоз      | CAK                |                                       |                          | 100                                               | 350                       | -                        |                     |                                  | 5-10 |

| M5M23C65-XXXP**  | 00005     | 64K                | 8K×8                                  |                          | 100                                               | 350                       |                          | 24P4                |                                  | 5-13 |

#### **EPROM**

| Туре           | Structure | Memory<br>capacity | Memory<br>configuration<br>(Word×Bit) | Supply<br>voltage<br>(V) | Typical<br>power<br>dissipation<br>(mW) | Access<br>time<br>Max(ns) | Type of<br>output | Package<br>outlines | Inter-<br>changeable<br>products | Page |

|----------------|-----------|--------------------|---------------------------------------|--------------------------|-----------------------------------------|---------------------------|-------------------|---------------------|----------------------------------|------|

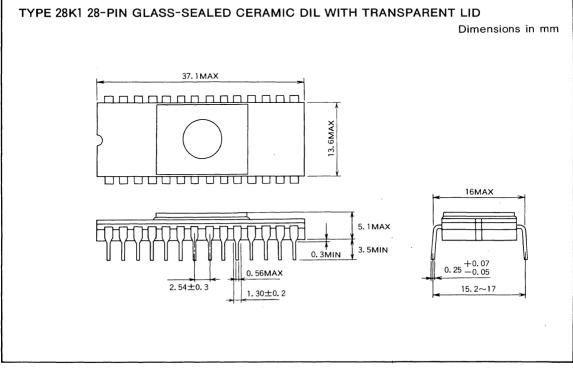

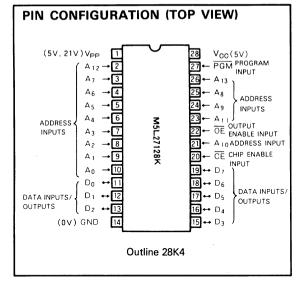

| M5L2764K-2     |           | 64K                | 8K×8                                  |                          | 300                                     | 200                       | _                 | - 28K1              | See                              | 6-3  |

| M5L2764K       | NMOS      | 041                | 01 0                                  |                          | 300                                     | 250                       | -                 | 2011                | page1-16                         | 0-3  |

| M5L27128K-2    |           |                    |                                       |                          | 350                                     | 200                       |                   |                     |                                  | 6-10 |

| M5L27128K      | 7         | 1                  |                                       | ,                        | 350                                     | 250                       |                   | ]                   |                                  | 0-10 |

| M5M27C128K-2** |           | 128K               | 16K×8                                 | 51500                    |                                         | 200                       |                   | ]                   | See                              |      |

| M5M27C128K**   | CMOS      |                    |                                       | 5±5%                     | 160                                     | 250                       | -                 | 28K4                | page1-16                         | 6—19 |

| M5M27C128K-3** | 7         |                    |                                       |                          |                                         | 300                       | -                 | 2014                |                                  |      |

| M5L27256K-2**  |           |                    |                                       |                          |                                         | 200                       | —                 | ]                   |                                  |      |

| M5L27256K**    | NMOS      | 256K               | 32K×8                                 |                          | 300                                     | 250                       | -                 |                     | i27256                           | _    |

| M5L27256K-3**  |           |                    |                                       |                          |                                         | 300                       | _                 |                     | i27256-3                         |      |

#### **EAROM**

| Туре      | Structure | Memory<br>capacity | Memory<br>configuration<br>(Word×Bit) | Supply<br>voltage<br>(V) | Typical<br>power<br>dissipation<br>(mW) | Access<br>time<br>Max(ns) | Cycle<br>time<br>Min(ns) | Package<br>outlines |        | Page |       |            |      |      |      |      |     |       |

|-----------|-----------|--------------------|---------------------------------------|--------------------------|-----------------------------------------|---------------------------|--------------------------|---------------------|--------|------|-------|------------|------|------|------|------|-----|-------|

| M58658P   |           | 320                | 20×16                                 | <b>%</b> 1               |                                         |                           | -                        |                     | —      | 7—15 |       |            |      |      |      |      |     |       |

| M58659P** | MNOS      | MNOS               | MNOS                                  | MNOS                     | MNOS                                    | MNOS                      | MNOS                     | MNOS                | MNOS   | 512  | 32×16 | <b>※</b> 1 |      |      | _    |      | —   | —     |

| M58653P   |           |                    |                                       |                          |                                         |                           |                          |                     |        | MNOS | MNOS  | MNOS       | MNOS | MNOS | MNOS | MNOS | 700 | 50×14 |

| M58657P   |           | 1400               | 1400 100 14                           | <b>※</b> 1               | -                                       |                           | —                        |                     |        | 7—9  |       |            |      |      |      |      |     |       |

| M5G1400P  |           | 1400               | 1400 100×14 -                         | <b>%</b> 2               | -                                       |                           | _                        |                     | ER1400 | 7-23 |       |            |      |      |      |      |     |       |

$%1 V_{GG} - V_{SS} = -35V \pm 8\%$ Vss-

$2 V_{GG} - V_{SS} = -35V \pm 8\%$

$$-V_{GND} = 5V_{-5\%}^{+20\%}$$

\*\* : Under development

MITSUBISHI LSIs

## **GUIDE TO INTERCHANGEABILITY**

|             | Mitsubishi<br>Electric | AMD<br>Advanced<br>Micro<br>Devices | G I<br>General<br>Instrument | FSC<br>Fairchild<br>Semiconductor | Fujitsu    | Hitachi     | INTEL<br>Intel | INTERSII<br>Intersil |

|-------------|------------------------|-------------------------------------|------------------------------|-----------------------------------|------------|-------------|----------------|----------------------|

|             | M5K4116P-2             | Am9016F                             |                              |                                   | MB8116H    | HM4716A-2   | 2117-2         |                      |

|             | M5K4116P-3             | Am9016E                             |                              |                                   | MB8116E    | HM4716A-3   | 2117-3         |                      |

|             | M5K4164AP-12           |                                     |                              |                                   | MB8265A-12 | HM4865AP-12 |                |                      |

|             | M5K4164AL-12           |                                     |                              |                                   |            |             |                |                      |

| 1           | M5K4164AP-15           | 1                                   |                              |                                   | MB8265A-15 | HM4865AP-15 |                |                      |

|             | M5K4164AL-15           |                                     |                              |                                   | -          |             |                |                      |

|             | M5K4164ANP-12          |                                     |                              |                                   | MB8264A-12 | HM4864AP-12 |                |                      |

|             | M5K4164ANP-15          |                                     |                              |                                   | MB8264A-15 | HM4864AP-15 |                |                      |

|             | M5K4164ANP-20          |                                     |                              |                                   |            |             |                |                      |

|             | M5K4164ANL-12          |                                     |                              |                                   |            |             |                |                      |

|             | M5K4164ANL-15          |                                     |                              |                                   |            |             |                |                      |

|             | M5K4164AND-12          |                                     |                              |                                   |            |             |                |                      |

|             | M5K4164AND-15          |                                     |                              |                                   |            | HM4864CC-2  |                |                      |

|             | MH6404AD1-15           |                                     |                              |                                   |            |             |                |                      |

|             | MH6408AD-15            |                                     |                              |                                   |            |             |                |                      |

| -           | MH6404AND1-15          |                                     |                              |                                   |            |             |                |                      |

| A           | MH6408AND-15           |                                     |                              | · ·                               |            |             |                |                      |

| L C         | M5M4416P-12            |                                     |                              |                                   | MB81416-12 |             |                |                      |

| š           | M5M4416P-15            |                                     |                              |                                   | MB81416-15 |             |                |                      |

| N N         | M5M4256S-12            |                                     |                              |                                   | MB81256-12 | HM50256-12  |                |                      |

| DYNAMIC RAM | M5M4256S-15            |                                     |                              |                                   | MB81256-15 | HM50256-15  |                |                      |

|             | M5M4256S-20            |                                     |                              |                                   |            | HM50256-20  |                |                      |

|             | M5M4257S-12            |                                     |                              |                                   | MB81257-12 | HM50257-12  |                |                      |

|             | M5M4257S-15            |                                     |                              |                                   | MB81257-15 | HM50257-15  |                |                      |

|             | M5M4257S-20            |                                     |                              |                                   |            | HM50257-20  |                |                      |

|             | M5M4256P-12            |                                     |                              |                                   | MB81256-12 | HM50256-12  |                |                      |

|             | M5M4256P-15            |                                     |                              |                                   | MB81256-15 | HM50256-15  |                |                      |

|             | M5M4256P-20            |                                     |                              |                                   |            | HM50256-20  |                |                      |

|             | M5M4257P-12            |                                     |                              |                                   | MB81257-12 | HM50257-12  |                |                      |

|             | M5M4257P-15            |                                     |                              |                                   | MB81257-15 | HM50257-15  |                |                      |

|             | M5M4257P-20            |                                     |                              |                                   |            | HM50257-20  |                |                      |

|             | M5M4256L-12            |                                     |                              |                                   |            |             |                |                      |

|             | M5M4256L-15            |                                     | •                            |                                   |            |             |                |                      |

| 1           | M5M4256L-20            |                                     |                              |                                   |            |             |                |                      |

|             | M5M4257L-12            |                                     |                              |                                   |            |             |                |                      |

|             | M5M4257L-15            |                                     |                              |                                   | 4          |             |                |                      |

|             | M5M4257L-20            |                                     |                              |                                   |            |             |                |                      |

|             | M5M4464P-12            |                                     |                              |                                   |            |             |                |                      |

|             | M5M4464P-15            |                                     |                              |                                   |            |             |                |                      |

| MOSTEK<br>Mostek | MOTOROLA<br>Motorola<br>Semiconductor<br>products | NSC<br>National<br>Semiconductor | Nippon<br>Electric | Oki                                   | TI<br>Texas<br>Instruments            | Toshiba      | Remarks |

|------------------|---------------------------------------------------|----------------------------------|--------------------|---------------------------------------|---------------------------------------|--------------|---------|

| MK4116-2         | MCM4116-15                                        | MM5290-2                         | μPD416-3           |                                       | TMS4116-15                            | TMM416P-2    |         |

| MK4116-3         | MCM4116-20                                        | MM5290-3                         | μPD416-2           |                                       | TMS4116-20                            | TMM416P-3    |         |

|                  |                                                   |                                  |                    |                                       |                                       |              |         |

|                  |                                                   |                                  |                    |                                       |                                       |              |         |

| MK4164N-15       |                                                   |                                  |                    |                                       |                                       |              |         |

|                  |                                                   |                                  | μPD4164C-12        |                                       |                                       |              |         |

| MK4564N-15       |                                                   |                                  | μPD4164C-15        |                                       | TMS4164-15NLJ                         | TMM4164P-3   |         |

|                  |                                                   |                                  |                    |                                       |                                       |              |         |

|                  |                                                   |                                  |                    |                                       |                                       |              |         |

|                  |                                                   |                                  |                    |                                       |                                       |              |         |

|                  |                                                   |                                  |                    |                                       |                                       |              |         |

|                  |                                                   |                                  |                    |                                       |                                       |              |         |

|                  |                                                   |                                  |                    |                                       |                                       |              |         |

|                  |                                                   |                                  |                    |                                       |                                       |              |         |

|                  |                                                   |                                  |                    |                                       |                                       |              |         |

|                  |                                                   |                                  |                    |                                       |                                       |              |         |

|                  |                                                   |                                  |                    |                                       | TMS4416-15                            |              |         |

| MK4556-12        |                                                   |                                  |                    | MSM41256-12                           | 1110441010                            | TMM41256C-12 |         |

| MK4556-15        |                                                   |                                  | μPD41256C/D-15     |                                       |                                       | TMM41256C-15 |         |

| MK4556-20        |                                                   |                                  | μPD41256C/D-20     |                                       |                                       |              |         |

|                  | MCM6257-12                                        |                                  |                    | MSM41257-12                           |                                       |              |         |

|                  | MCM6257-15                                        |                                  | μPD41257C/D-15     | MSM41257-15                           |                                       |              |         |

|                  |                                                   |                                  | μPD41257C/D-20     | MSM41257-20                           |                                       |              |         |

| MK4556-12        |                                                   |                                  |                    | MSM41256-12                           |                                       | TMM41256C-12 |         |

| MK4556-15        |                                                   |                                  | μPD41256C/D-15     |                                       |                                       | TMM41256C-15 |         |

|                  |                                                   |                                  | .μPD41256C/D-20    |                                       |                                       |              |         |

|                  | MCM6257-12                                        |                                  |                    | MSM41257-12                           |                                       |              |         |

|                  | MCM6257-15                                        |                                  | μPD41257C/D-15     |                                       |                                       |              |         |

|                  |                                                   |                                  | μPD41257C/D-20     | MSM41257-20                           |                                       |              |         |

|                  |                                                   |                                  |                    |                                       |                                       |              |         |

|                  |                                                   |                                  |                    |                                       |                                       |              |         |

|                  |                                                   |                                  |                    |                                       | · · · · · · · · · · · · · · · · · · · |              |         |

|                  |                                                   |                                  |                    | · · · · · · · · · · · · · · · · · · · |                                       |              |         |

|                  |                                                   |                                  |                    |                                       |                                       |              |         |

|                  | ×                                                 |                                  |                    |                                       |                                       |              |         |

|                  | · · · ·                                           |                                  |                    |                                       |                                       |              |         |

#### **MITSUBISHI LSIs**

## **GUIDE TO INTERCHANGEABILITY**

|        | Mitsubishi<br>Electric | AMD<br>Advanced<br>Micro<br>Devices | AMI<br>American<br>Microsystems | FSC<br>Fairchild<br>Semiconductor | Fujitsu    | Hitachi     | INTEL<br>Intel | INTERSIL<br>Intersil |

|--------|------------------------|-------------------------------------|---------------------------------|-----------------------------------|------------|-------------|----------------|----------------------|

|        | M58725P-15             |                                     |                                 |                                   | MB8128-15  |             |                |                      |

|        | M58725P                |                                     |                                 |                                   |            |             |                |                      |

|        | M5M2167P-55            | Am2167-55                           |                                 |                                   | MB8167A-55 | HM6167H-55  | i2167-55       |                      |

|        | M5M2167P-70            | Am2167-70                           |                                 |                                   | MB8167A-70 | HM6167H-70  | i2167-70       |                      |

|        | M5M2168P-55            |                                     |                                 |                                   | MB8168-55  | HM6168H-55  |                |                      |

|        | M5M2168P-70            |                                     |                                 |                                   | MB8168-70  | HM6168H-70  |                |                      |

|        | M5M5116P-15            |                                     |                                 |                                   | MB8417-15  |             |                |                      |

|        | M5M5116P               |                                     |                                 |                                   | MB8417-20  |             |                |                      |

|        | M5M5116FP-15           |                                     |                                 |                                   |            |             |                |                      |

|        | M5M5116FP              |                                     |                                 |                                   | -          |             |                |                      |

| 5      | M5M5117P-15            |                                     |                                 |                                   | MB8416-15  | HM6116L-3   |                |                      |

| RAM    | M5M5117P               |                                     |                                 |                                   | MB8416-20  | HM6116L-4   |                |                      |

|        | M5M5117FP-15           |                                     |                                 |                                   |            | HM6116LFP-3 |                |                      |

| STATIC | M5M5117FP              |                                     |                                 |                                   |            | HM6116LFP-4 |                |                      |

| E.     | M5M5118P-15            |                                     |                                 |                                   |            | HM6117LP-3  |                |                      |

| S.     | M5M5118P               |                                     |                                 |                                   | MB8418-20  | HM6117LP-4  |                |                      |

|        | M5M5118FP-15           |                                     |                                 |                                   |            | HM6117LFP-3 |                |                      |

|        | M5M5118FP              |                                     |                                 |                                   |            | HM6117LFP-4 |                |                      |

|        | M5M5165P-70<br>/P-70L  |                                     |                                 |                                   |            |             |                |                      |

|        | M5M5165P-10            |                                     |                                 |                                   |            | HM6264P-10  |                |                      |

|        | /P-10L                 |                                     |                                 |                                   |            | /LP-10      |                |                      |

|        | M5M5165P-12            |                                     |                                 |                                   | MB8464-12  | HM6264P-12  |                |                      |

|        | /P-12L                 |                                     |                                 |                                   | /-12L      | /LP-12      |                |                      |

|        | M5M5165P-15            |                                     |                                 |                                   | MB8464-15  | HM6264P-15  |                |                      |

|        | /P-15L                 |                                     |                                 |                                   | /-15L      | /LP-15      |                |                      |

AMD AMI FSC Mitsubishi Advanced INTEL INTERSIL Hitachi Fujitsu American Fairchild Electric Micro Intel Intersil Microsystems Semiconductor Devices M5M2364-XXXP ROM M5M23C64-XXXP M5M2365-XXXP MASK M5M23C65-XXXP M5M23128-XXXP M5M23256-XXXP M5M231000-XXXP

| MOSTEK<br>Mostek | MOTOROLA<br>Motorola<br>Semiconductor<br>products | NSC<br>National<br>Semiconductor | Nippon<br>Electric                                           | Oki                          | TI<br>Texas<br>Instruments | Toshiba              | Remarks |

|------------------|---------------------------------------------------|----------------------------------|--------------------------------------------------------------|------------------------------|----------------------------|----------------------|---------|

|                  |                                                   |                                  | μPD4016C-3                                                   | MSM2128-15                   |                            | TMM2016P             |         |

|                  |                                                   |                                  | μPD4016C-2                                                   | MSM2128-20                   |                            | TMM2016P-2           |         |

|                  |                                                   |                                  | μPD2167D-3                                                   |                              |                            |                      |         |

|                  |                                                   |                                  | μPD2167D-2                                                   |                              |                            |                      |         |

| •                |                                                   |                                  |                                                              |                              | ×                          |                      |         |

|                  |                                                   |                                  | μΡD447C-3<br>μΡD447C-2                                       | MSM5127-15RS<br>MSM5127-20RS |                            | TC5516AP             | -       |

|                  |                                                   |                                  |                                                              |                              |                            | TC5516AFP            |         |

|                  |                                                   |                                  | μPD446C-3                                                    | MSM5128-15RS                 |                            |                      |         |

|                  |                                                   |                                  | μPD446C-2                                                    | MSM5128-20RS                 |                            | TC5517AP             |         |

|                  |                                                   |                                  |                                                              |                              |                            | TC5517AFP            |         |

|                  |                                                   |                                  | μPD449C-3                                                    | MSM5129-15RS                 |                            |                      |         |

| -touch and       |                                                   |                                  | μPD449C-2                                                    | MSM5129-20RS                 |                            | TC5518BP             |         |

|                  |                                                   |                                  |                                                              |                              |                            | TC5518BF             |         |

|                  |                                                   |                                  |                                                              |                              |                            |                      |         |

|                  |                                                   |                                  |                                                              |                              |                            |                      |         |

|                  |                                                   |                                  |                                                              | MSM5165-12RS                 |                            | TC5565P-12<br>/PL-12 |         |

|                  |                                                   |                                  | μPD4364C-15/<br>C-15L(150ns)<br>μPD4364C-20/<br>C-20L(200ns) | MSM5165-15RS                 |                            | TC5565P-15<br>/PL-15 |         |

| MOSTEK<br>Mostek | MOTOROLA<br>Motorola<br>Semiconductor<br>products | NSC<br>National<br>Semiconductor | Nippon<br>Electric | Oki | TI<br>Texas<br>Instruments | Toshiba | Remarks |

|------------------|---------------------------------------------------|----------------------------------|--------------------|-----|----------------------------|---------|---------|

| MK37000          |                                                   |                                  |                    |     |                            |         |         |

| MK36000          |                                                   |                                  |                    |     |                            |         | 24pin   |

|                  |                                                   |                                  | μPD23128           |     |                            |         |         |

| MK38000          |                                                   |                                  |                    |     |                            |         |         |

|                  |                                                   |                                  |                    |     |                            |         | 28pin   |

|      | Mitsubishi<br>Electric | AMD<br>Advanced<br>Micro<br>Devices | AMI<br>American<br>Microsystems | FSC<br>Fairchild<br>Semiconductor | Fujitsu      | Hitachi                               | INTEL<br>Intel | INTERSIL<br>Intersil |

|------|------------------------|-------------------------------------|---------------------------------|-----------------------------------|--------------|---------------------------------------|----------------|----------------------|

|      | M5L2764K-2             |                                     |                                 |                                   | MBM2764-20   |                                       | D2764-2        |                      |

|      | M5L2764K               |                                     |                                 |                                   | MBM2764-25   | HN482764G                             | D2764          |                      |

|      | M5L27128K-2            |                                     |                                 |                                   |              | · · · · · · · · · · · · · · · · · · · |                |                      |

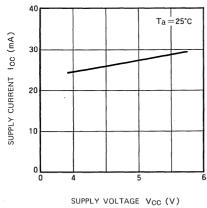

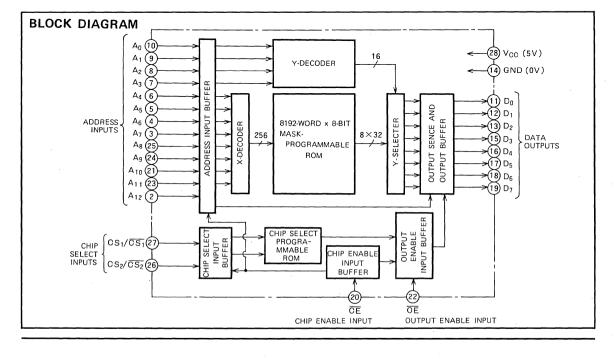

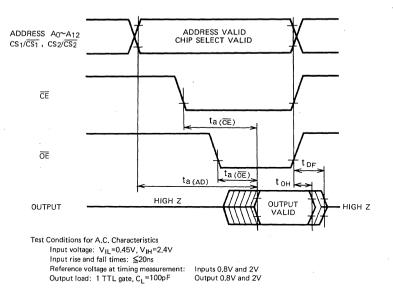

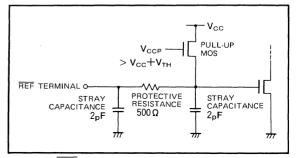

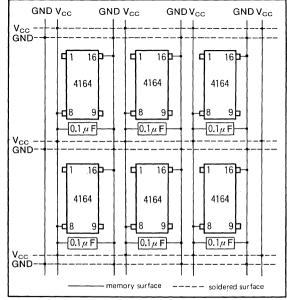

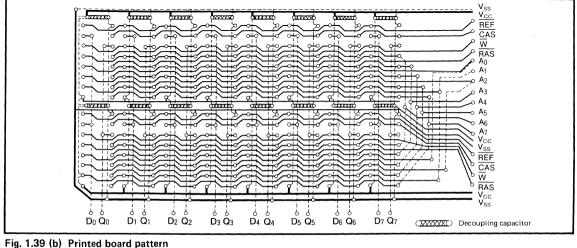

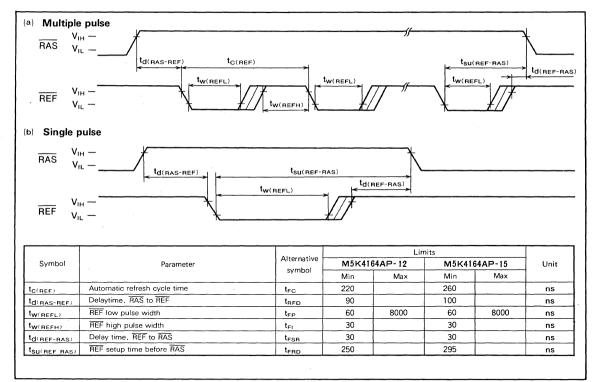

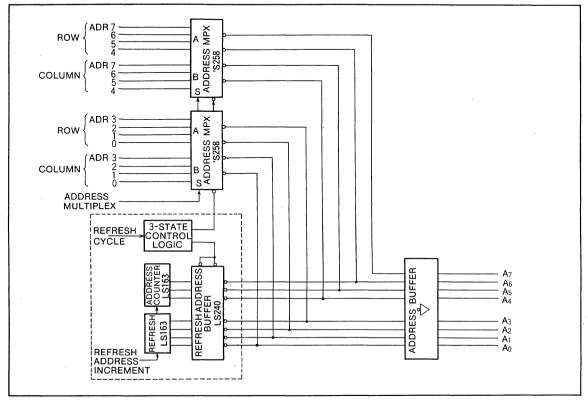

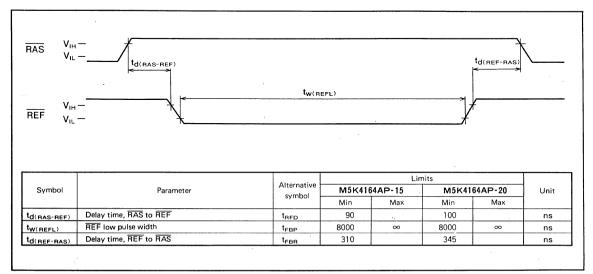

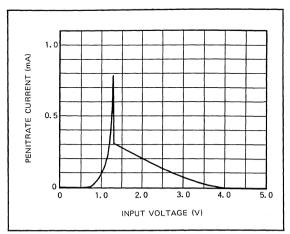

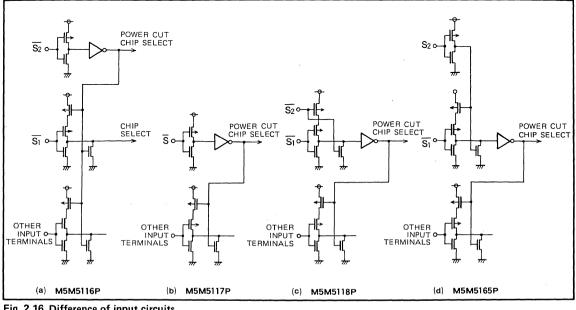

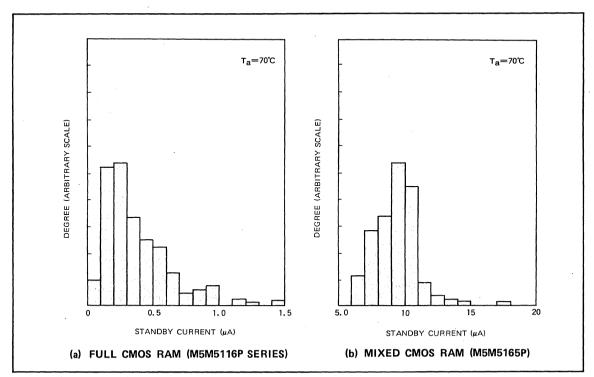

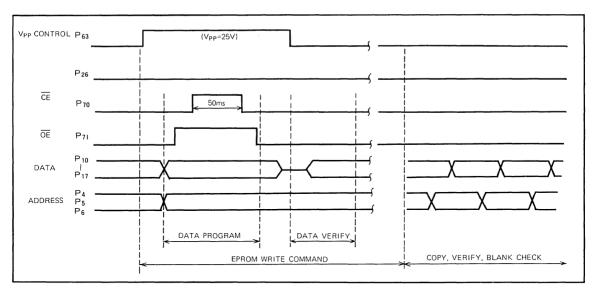

| -    | M5L27128K              | Am27128-25                          |                                 |                                   | MBM27128-25  | HN4827128-25                          | D27128         |                      |